Optical Sensor Development

基础技能

- ARM架构芯片的样例代码加载、编译、烧录、调试工作熟悉。

- bitbucket 如何使用(是否需要配置SSH、repository如何pull和push、add、commit等) √

- confluence 如何使用(任务的查看、提交、文章的发布、协作等等)

IDE for Realtek

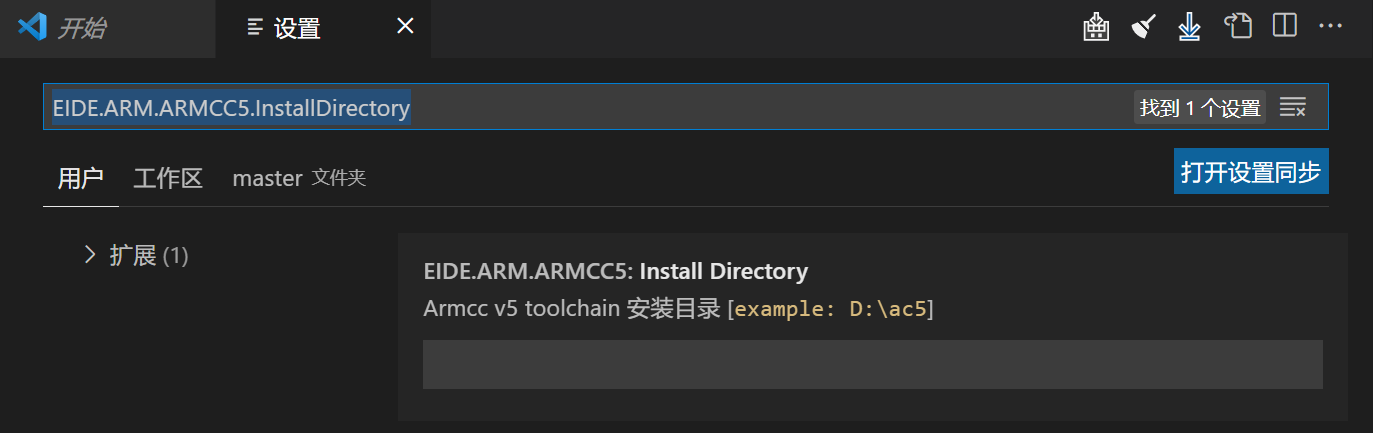

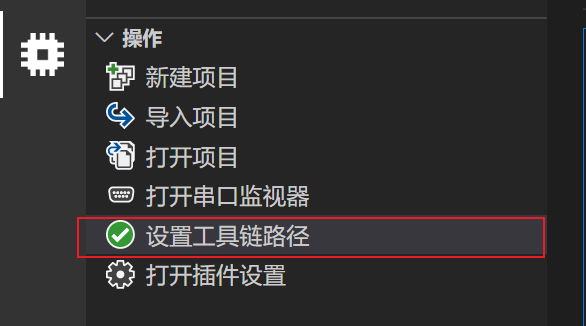

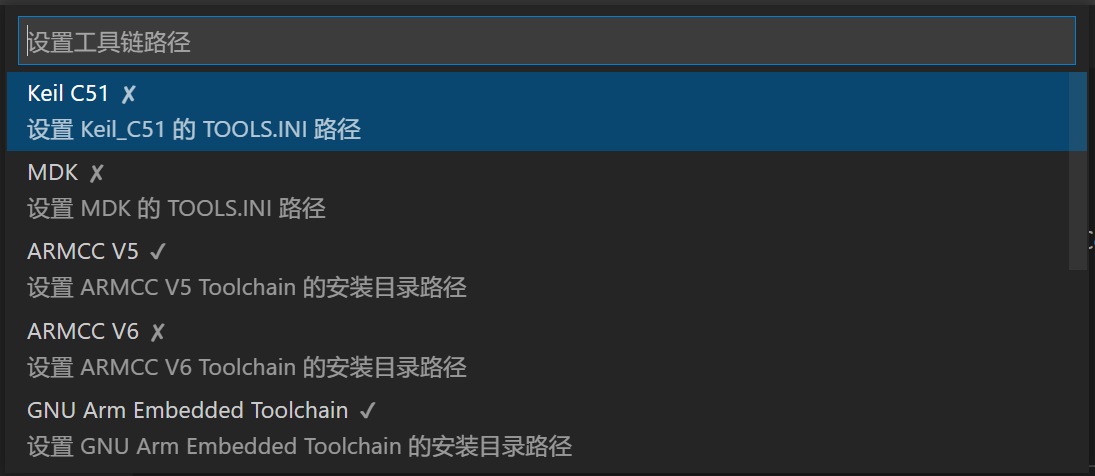

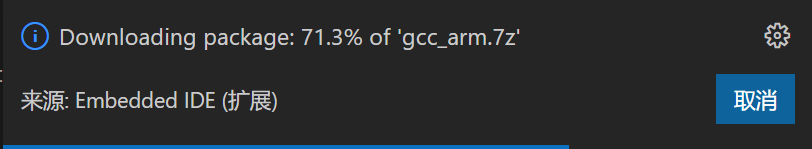

VSCODE ARM

KEIL ARM

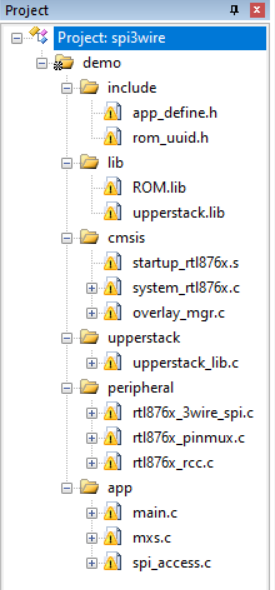

将Realtek RTL8762D SDK中的项目单独摘出来,放到某个文件夹下进行管理时,需要单独更改好几处内容:

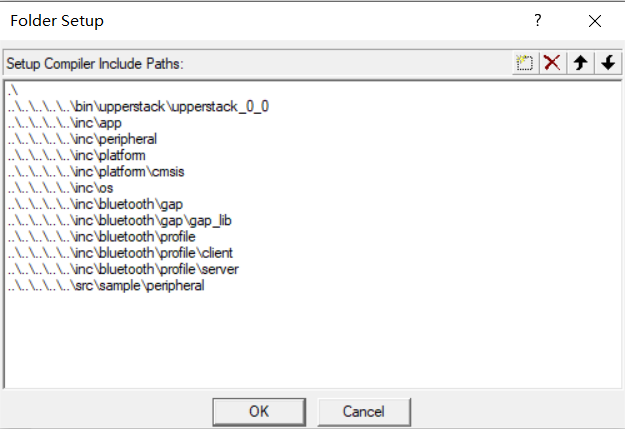

- C/C++的Include Path

- 源文件的Source Path

- APP Image(

.bin生成文件),即after_build_common.bat的路径和内容。

如下所示,把单独某个Project摘出来时会产生很多感叹号。

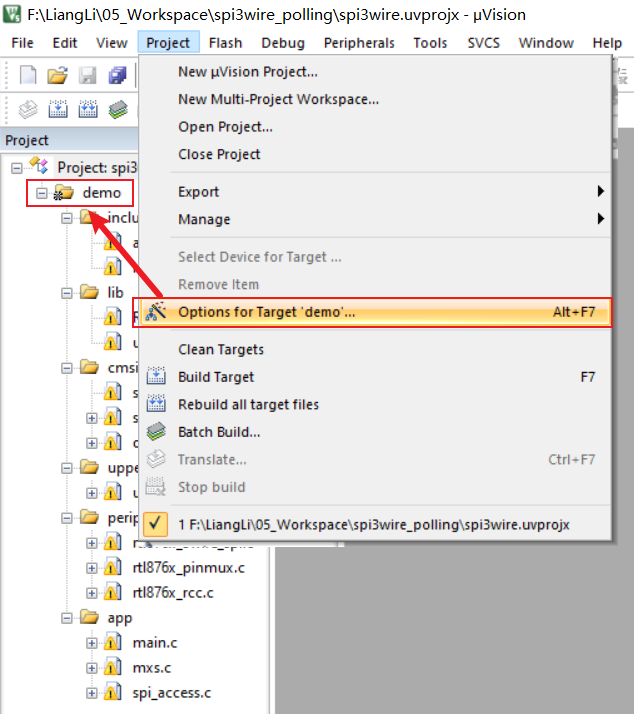

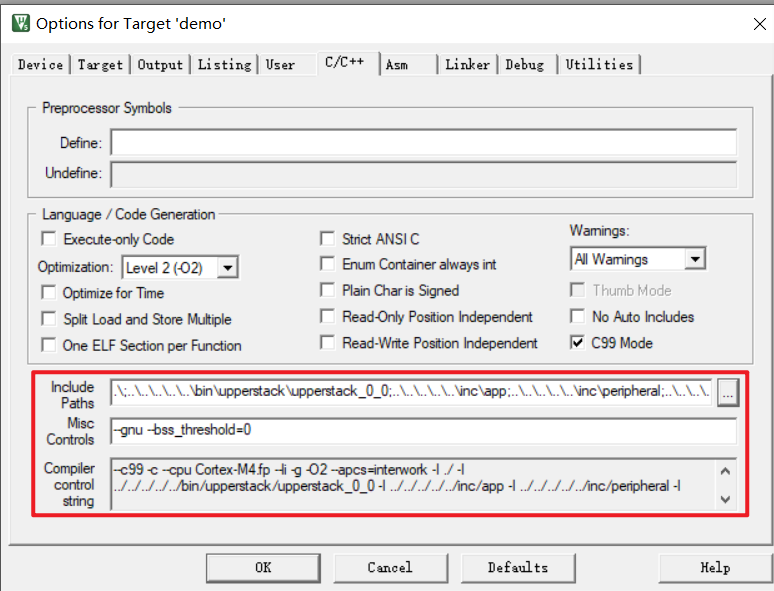

头文件路径修改

此时需要进入设置中进行头文件路径修改

选择 C/C++ 选项卡下的 Include Paths

进行修改。

原来的路径设置都是使用相对路径进行的,此时需要将

sbee2-sdk-v1.0.0

文件夹放到与你项目文件同盘的某个文件夹下,最好不要相距太远。

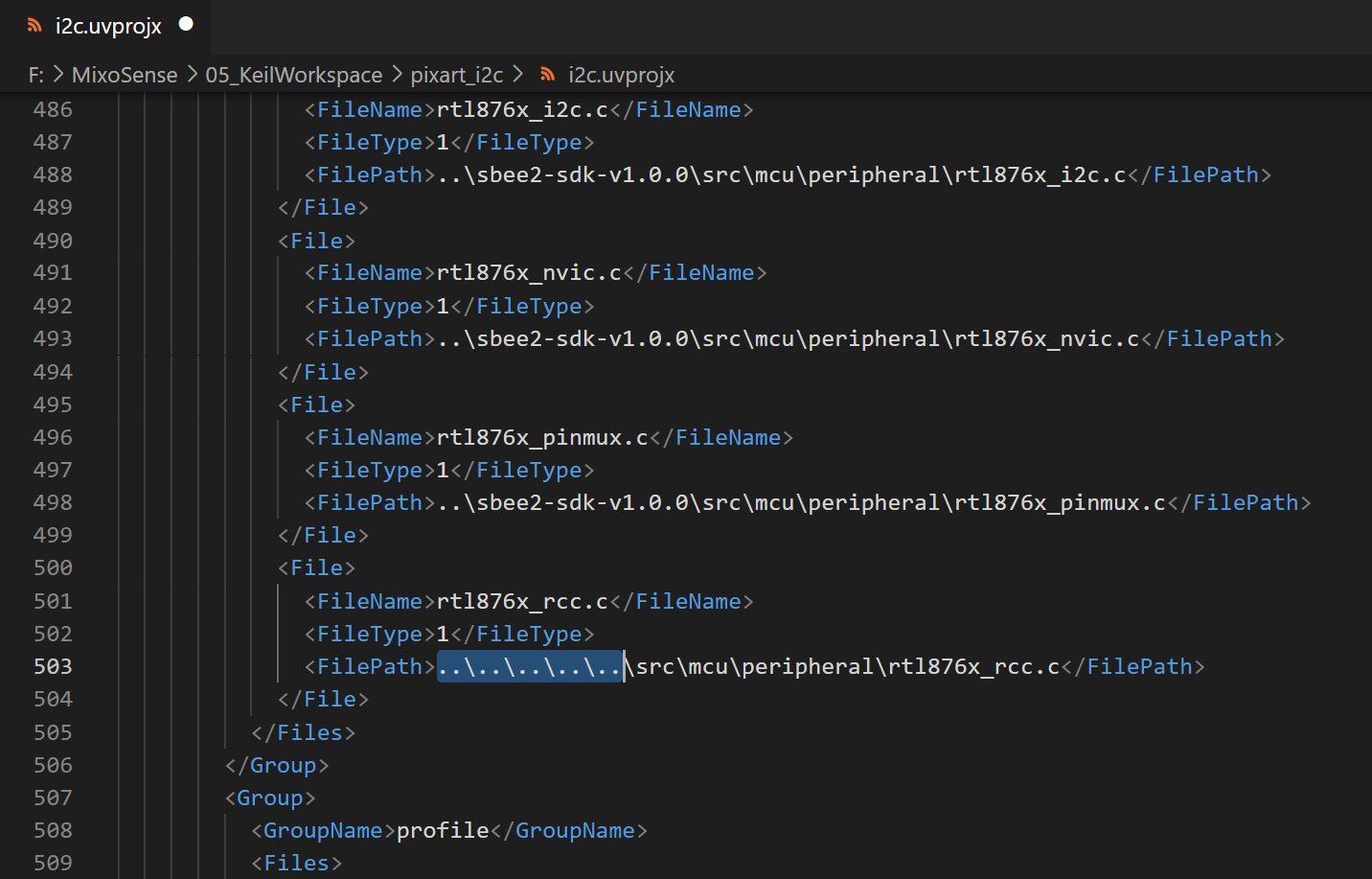

可以使用 VS Code将 .uvprojx

文件打开,使用搜索和替换工具对相关头文件的路径进行替换。

源文件路径修改

修改方法同头文件,

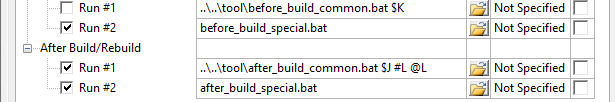

bat文件路径修改

.bat 文件是用于在 .o

文件生成后的链接脚本。所以如果该脚本自身路径和脚本内的包含路径出错,可能会导致无法编译出对应的

app_MP_adk##### 文件。

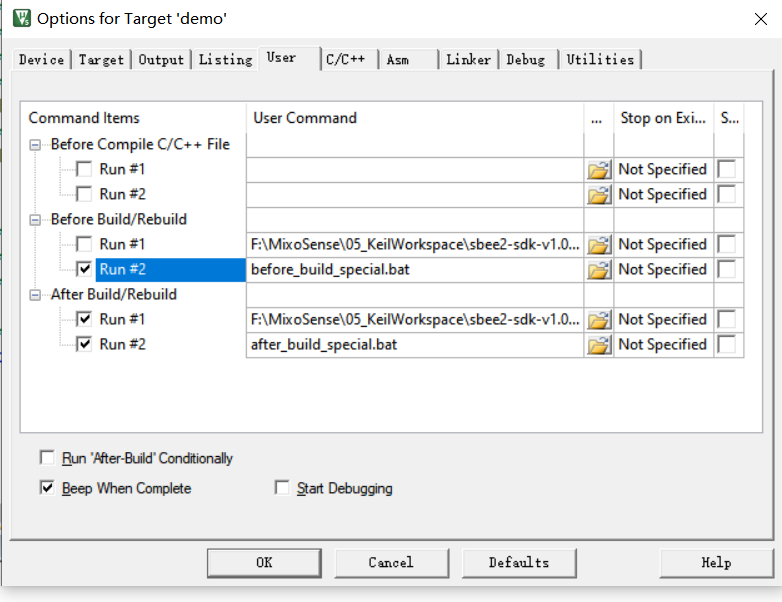

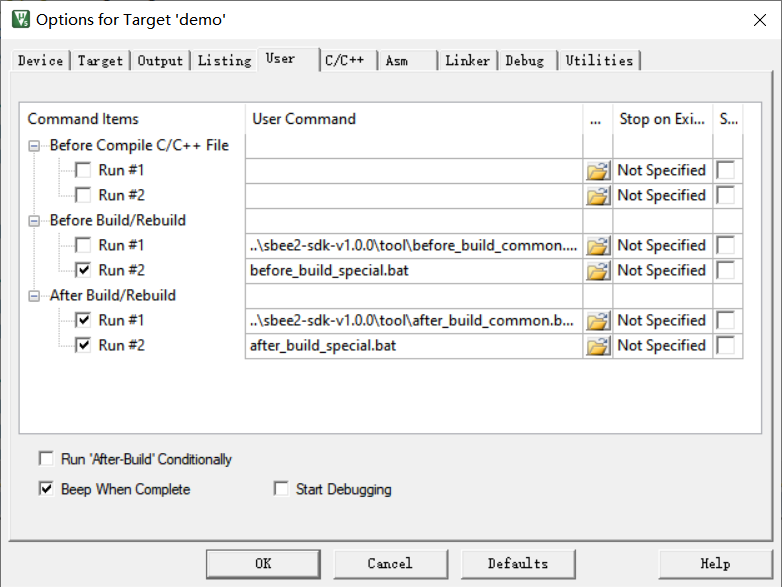

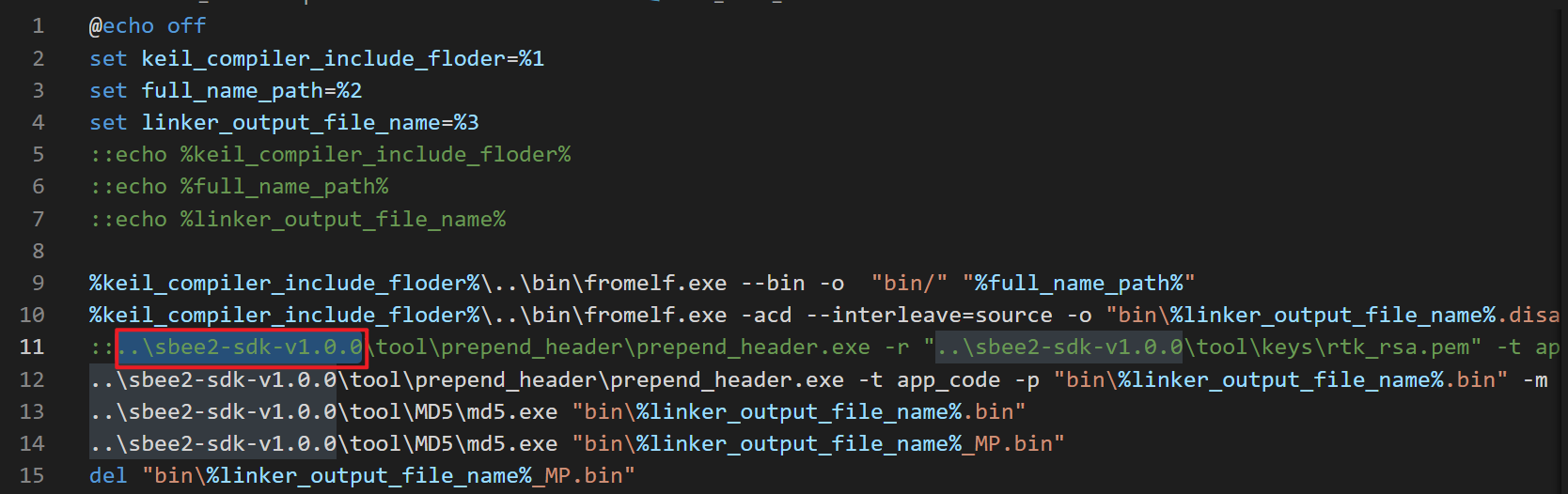

下方为样例代码原来的设置情况:

在 Option-User 设置中,可以查看到

After Build/Rebuild 相关的设置,其中 Run #1

则是 Realtek MP Tools 需要烧录 EVB开发板相关的脚本文件。

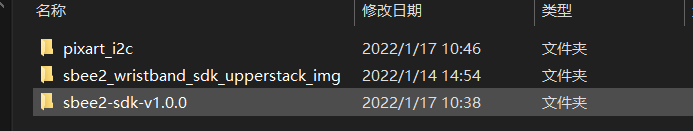

将单独摘放出来的项目文件夹 pixart_i2c 与

sbee2-sdk-v1.0.0 和

sbee2_wristband_sdk_upperstack_img 放到同一个文件夹下。

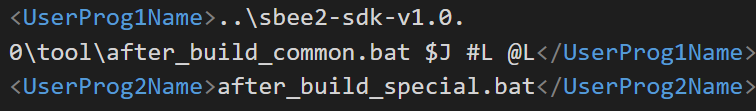

因此修改 .uvprojx 文件内容下

after_build_common.bat

的路径时,将该路径修改为如下的相对路径即可:

1 | ..\sbee2-sdk-v1.0.0\tool\after_build_common.bat $J #L @L |

保存修改后的 .uvprojx 文件,可以看到 Keil V5

自动更新了相关设置。如下:

after_build_common.bat 控制着自动生成Realtek 的 MP Tool

需要使用的 APP Bin文件,如果该 Run #1

没有启用,则无法生产该文件。

该.bat 文件下所有的 ..\..\..\tool\

都要修改成

..\sbee2-sdk-v1.0.0\tool\,如果项目文件夹和SDK文件夹路径有异,则需要适当修改。

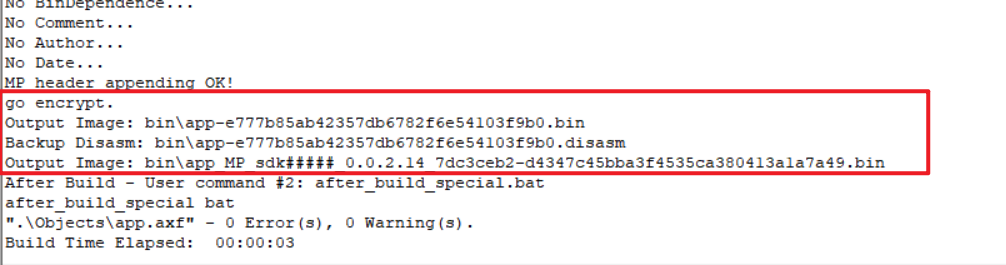

启用完成之后即可生成对应 app_MP_adk##### 文件

HARDWARES

ADAPTER

SPECIFICATION

A4芯片,即KA8G2芯片用的转接板需要接入5V电压,LDO会转换电压。

而PAT9126JA芯片则使用两个3.3V进行接入。

CHIP & BOARD

开发测试板为 Realtek RTL8762D EVB KIT。

型号: RTL8762DW

SENSOR - KA8G2

KAG2 is a high performance and ultra low power CMOS-processed optical image sensor with integrated digital image process circuits. It is based on an optical navigation technology which measures changes in position by optically acquiring sequential surface images(frames) and mathematically determining the speed, the direction and the magnitude of motion. The displacement delta_X and delta_Y information are available in registers which are accessible through SPI serial interface. A host controller reads and translates the data from the SPI serial interface into RF signals before sending them to the host PC.

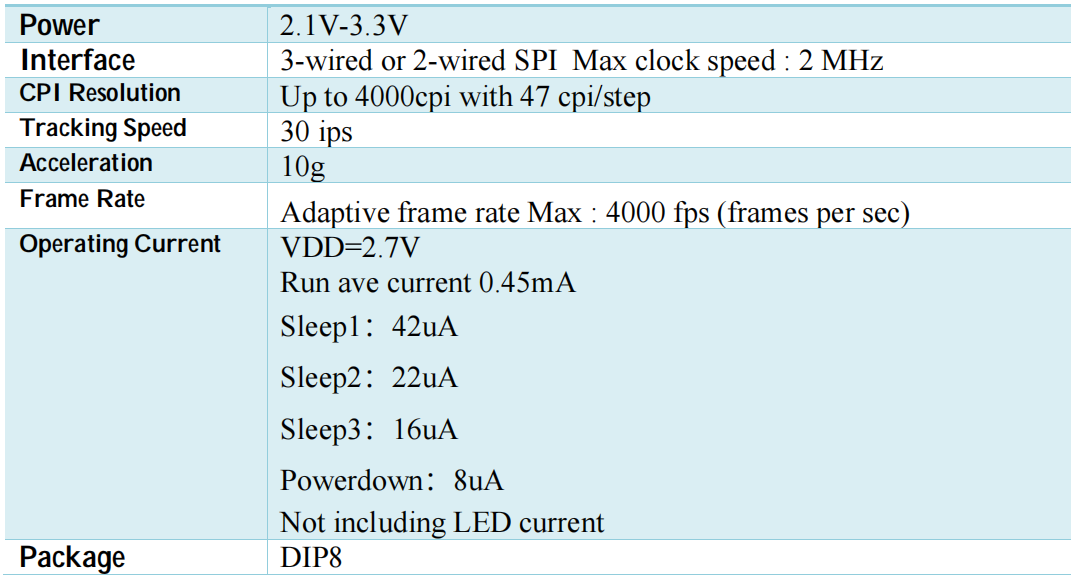

SPECIFICATION

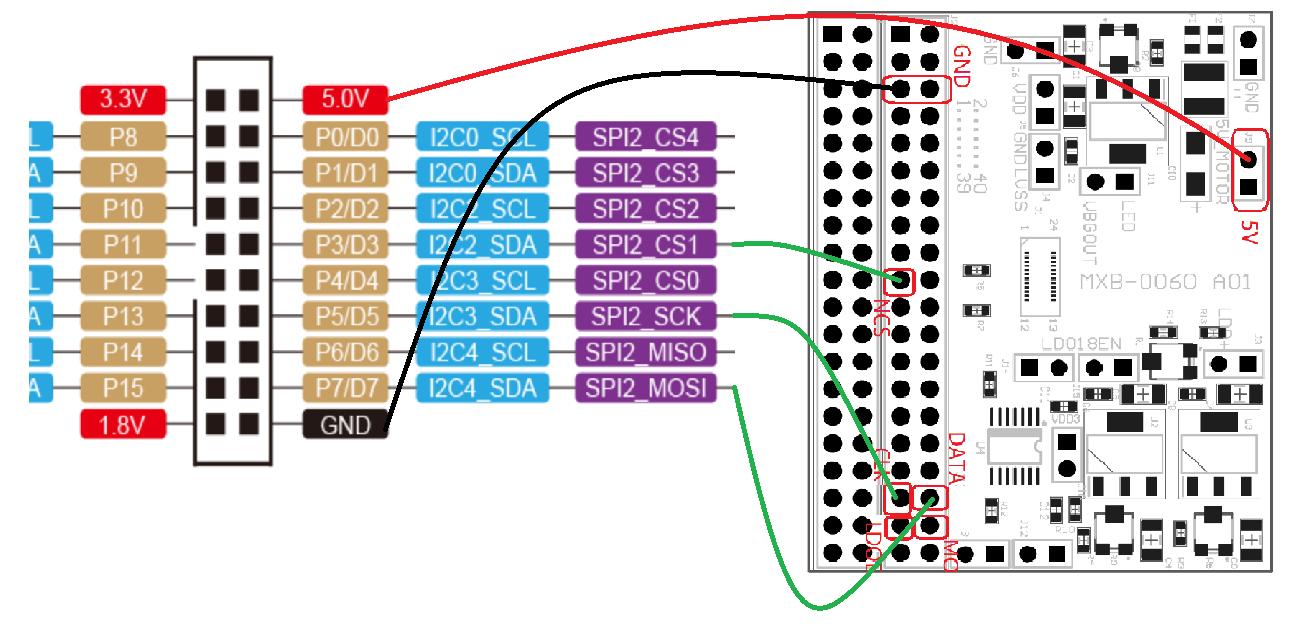

HARDWARE LINKING

CHIP INITIATE

这个芯片启动时,需要对一些寄存器进行写入以初始化。下方为二维数组,sensor_init_regs[][0]

为寄存器地址,sensor_init_regs[][1]

为寄存器需要写入的数据。

1 | uint8_t sensor_init_regs[7][2] = { |

初始化时,需要注意以下问题:

- 某些主控芯片在使用两线SPI进行数据写入时,会有要求使用

7bit地址,且 MSB 为1。此时需要判断是否需要认为修改地址的 MSB为1,例如 Realtek 的 RTL8762DW 芯片就不需要人为修改,人为修改会导致波形异常。而某些芯片需要人为写入MSB。 - 在每一次写入寄存器之后,强烈建议进行延时,可以使用

delay(0xFFFF),(尝试过0xFF太短,不能完成初始化写入)。

SENSOR - PAT9126JA

- 需要确定

ID_SEL引脚的连接情况,是拉高、接地还是悬空。分别对应的CHIP ID都是不一样的,可能是0x730x750x79三者之一。

transformer 上的 VCC 为 3.3V

SPECIFICATION

这个芯片有两种电压要求,默认为高电压版本 3.3V

,可以通过SPI写入寄存器和硬件并线来达到降低至 1.8V

低电压的模式。

HADWARE LINKING

SDK & Tools

此处有 2个SDK包 和 3个tool包,分别是:

- sbee2-sdk-v1.0.0.zip

- sbee2_wristband_sdk_upperstack_img.zip

- MPPackTool_v2.0.5.2.zip

- 日志输出软件:DebugAnalyzer-v4.0.0.14.zip

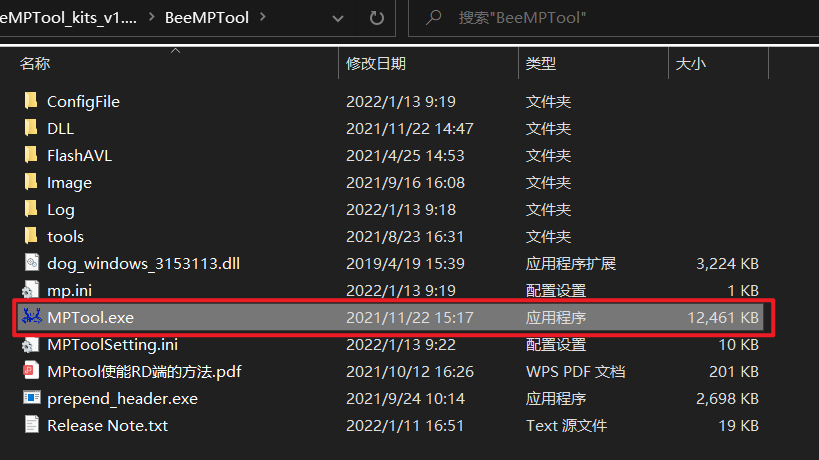

- 代码烧录软件:BeeMPTool_kits_v1.0.5.0.zip

BUILD / FLASH / LOG

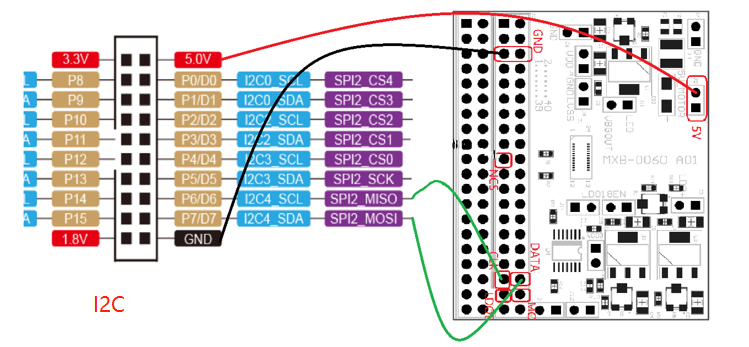

BUILD

点击 build 按钮即可进行代码构建。

build 完毕之后可以看到下方的成功提示

0 Error(s), 0 Warning(s)。

FLASH

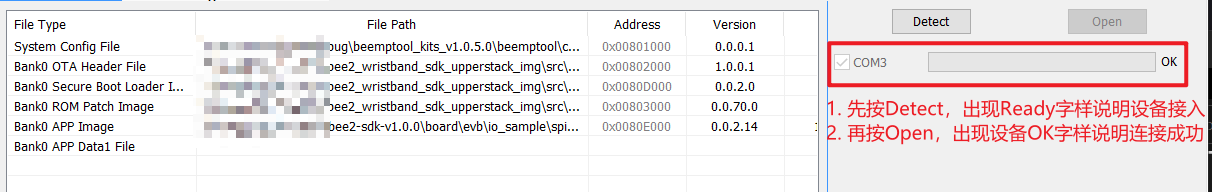

FLAHS需要经过 configuration 、 detect 和 download 三步

configuration

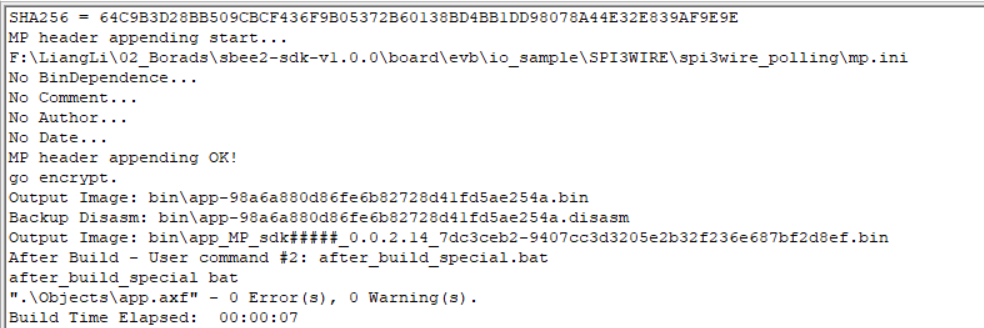

根据《RTL8762D SDK User Guide CN》文件,RTL8762D 的 EVB KIT 是可以支持 JLINK 的(如下图所示)。

但这里并未使用 JLINK,而是使用 Realtek 专门的工具

BeeMPTool_kits, 通过 UART 进行烧录。

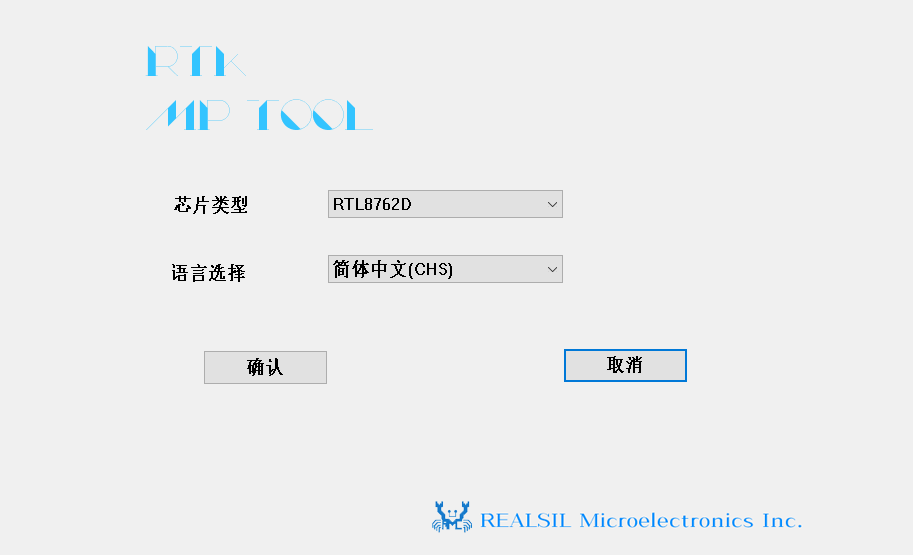

打开 MPTool.exe ,并选中对应的芯片型号

RTL8762D :

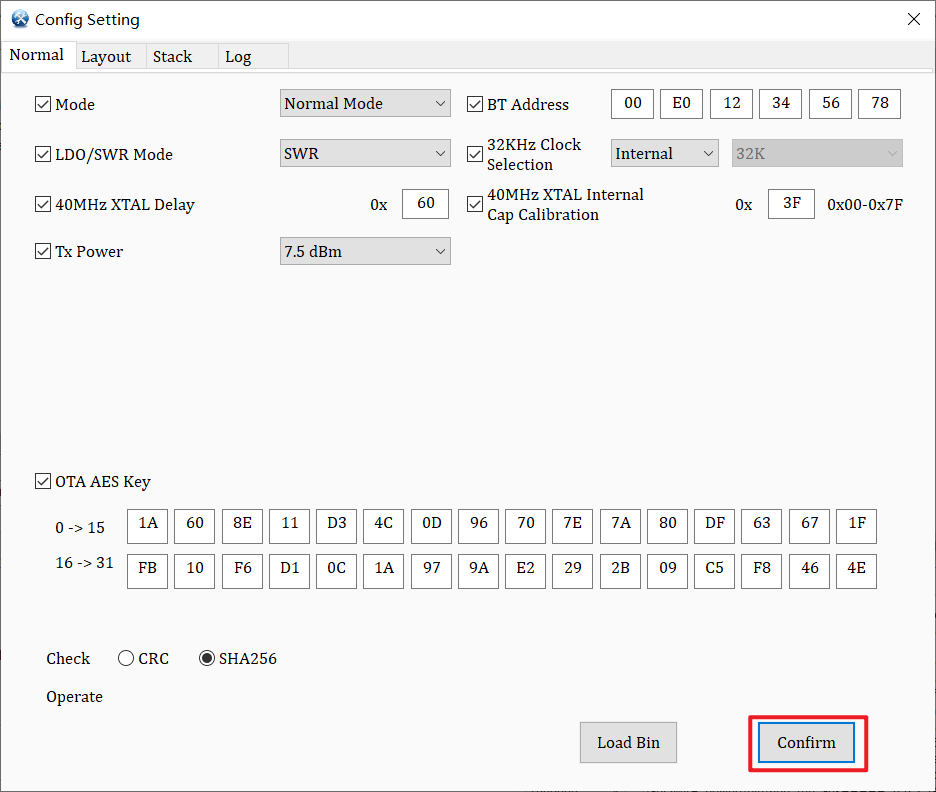

在这里选择 调试 模式进行烧录

在 Config Set 中选择 Confirm

,不需要修改什么东西。

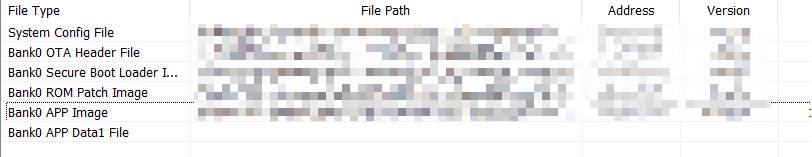

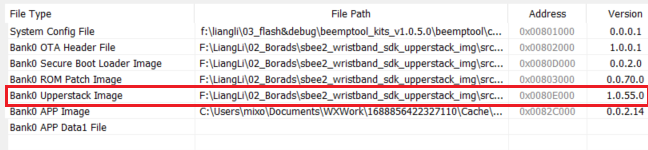

此处需要设置 Flash 地址映射文件 flash map.ini 。

下方为 《RTL8762D SDK User Guide CN》文件中,9.1章节对五个images文件进行了描述。

| FILE TYPE | DESCRIPTION | FILE PATH |

|---|---|---|

| System Config File | - 来自 BeeMPTool_kits |

\BeeMPTool_kits_v1.0.5.0\BeeMPTool\ConfigFile\ |

| Bank0 OTA Header File | - 来自 sbee2_wristband_sdk_upperstack_img |

\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\ |

| Bank0 Secure Boot Loader Image | - 来自 sbee2_wristband_sdk_upperstack_img |

\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\ |

| Bank0 ROM Patch Image | - 来自 sbee2_wristband_sdk_upperstack_img |

\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\ |

| Bank0 APP Image | - 来自 sbee2-sdk-v1.0.0 |

sbee2-sdk-v1.0.0\board\evb\io_sample\SPI3WIRE\spi3wire_polling\bin |

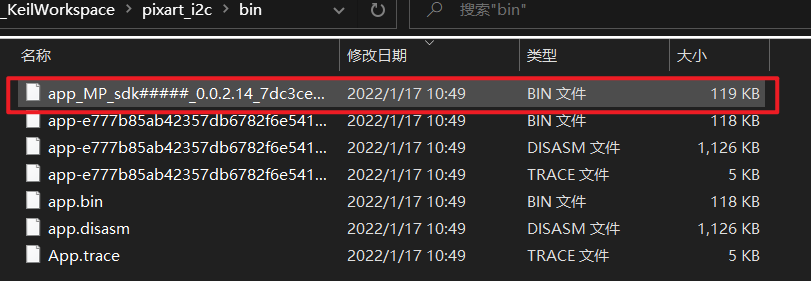

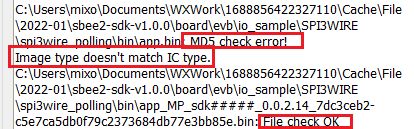

关于app image文件选择

在Build完成后,会生成三个 .bin

文件,如果选择错误,会提示

MD5 check error!Image type doesn't match IC type.

,选择正确的话会提示 File check OK 。

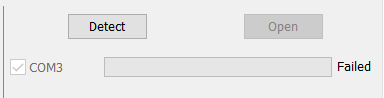

detect

detect 的时候需要注意:

- 将 EVB kit上的

J15LOG口接地,否则会检测失败 - 如果出现

Failed字样,则按一下 EVB KIT 上的红色的RESET按钮进行复位后再尝试。

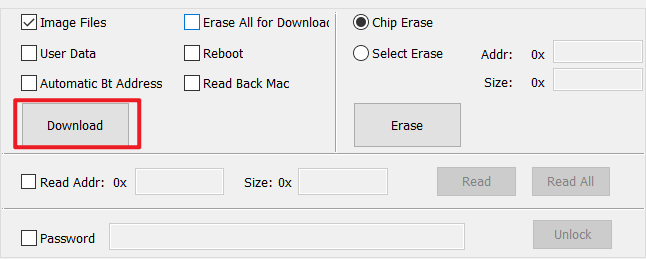

download

最后选择 download 下载即可。

UPPERSTACK FLASH

自带的 \sbee2-sdk-v1.0.0\doc\ 路径下的教程是,都是有

Bank0 Upperstack Image 需要烧录的。

步骤如下:

使用

\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\upperstack_img路径下的.ini文件作为 layout 文件。(而之前使用的flash map.ini地址为\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\)指定

\sbee2_wristband_sdk_upperstack_img\src\app\wristband\firmware\upperstack_img路径下的.bin文件作为 Upperstack Image 文件。将

\sbee2_wristband_sdk_upperstack_img\board\evb_stack_img\wristband\flash_map.h文件作为项目工程里的唯一内存映射文件依赖。flash_map.h被放在mem_config.h头文件下,间接被syetem_rtl876x.h引用。

LOG

RTL8762D 的 EVB KIT 不支持 JTAG 方式进行观察,(听说是)通信过程容易被打断。

这里使用 UART 和 EVB KIT 上的 J15 口来观察

LOG数据。

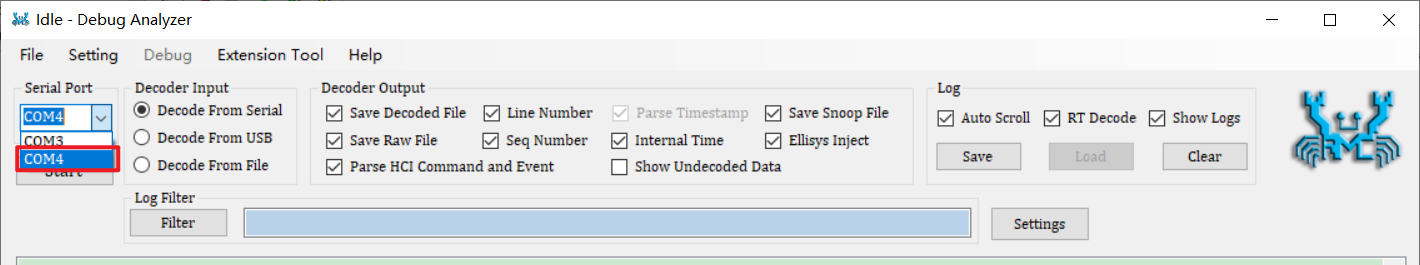

LOG软件

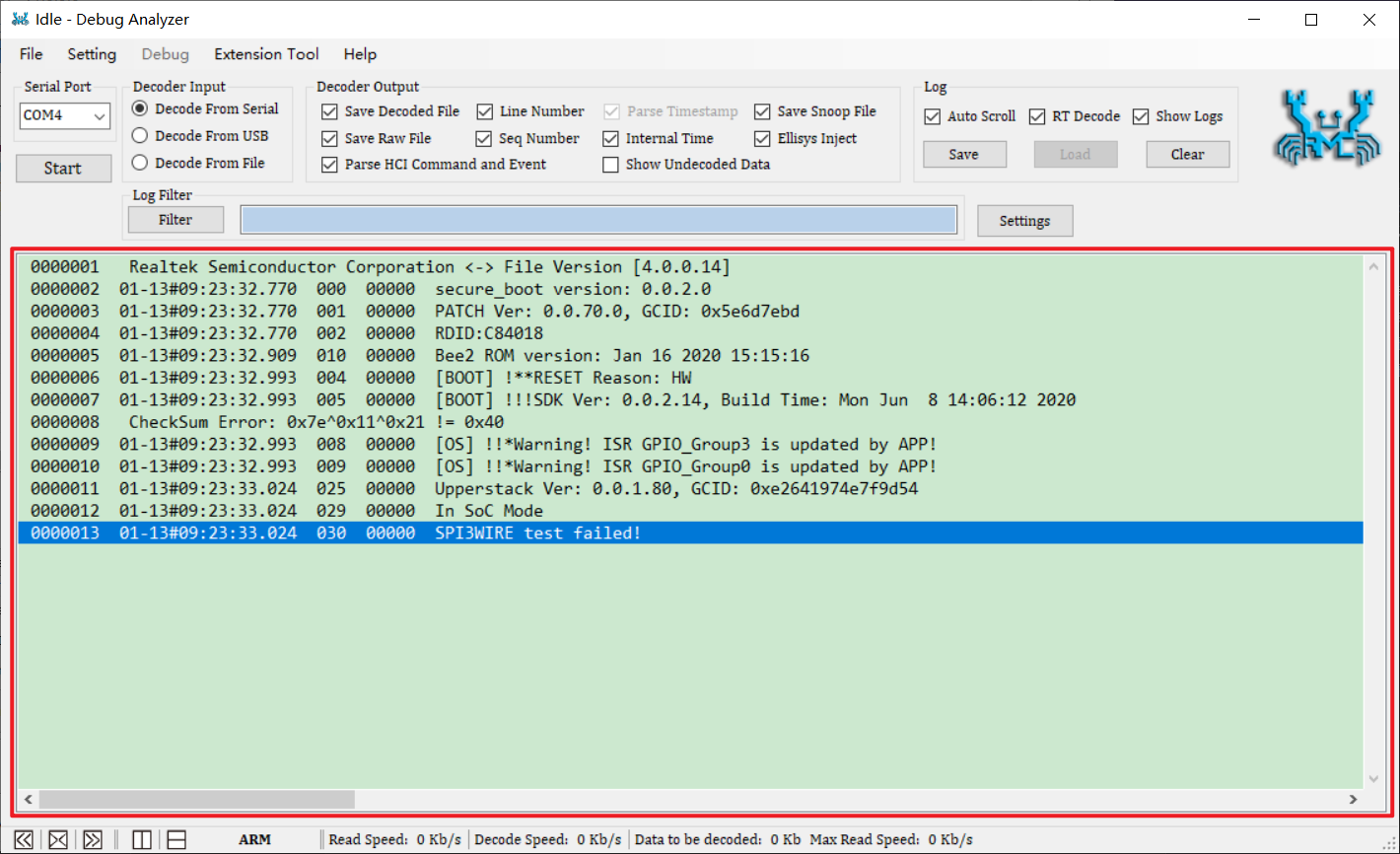

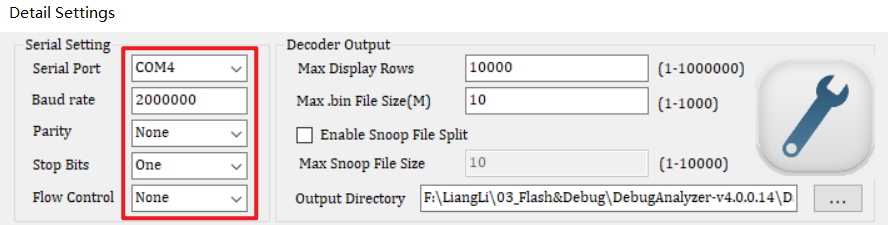

使用专用工具 DebugAnalyzer 进行日志输出。

- 选择合适的串口,即使用

FT232的UART口,将该芯片口的RX连接至RTL8762D板子上的J15口。并在电脑中选中对应的FT232设备。

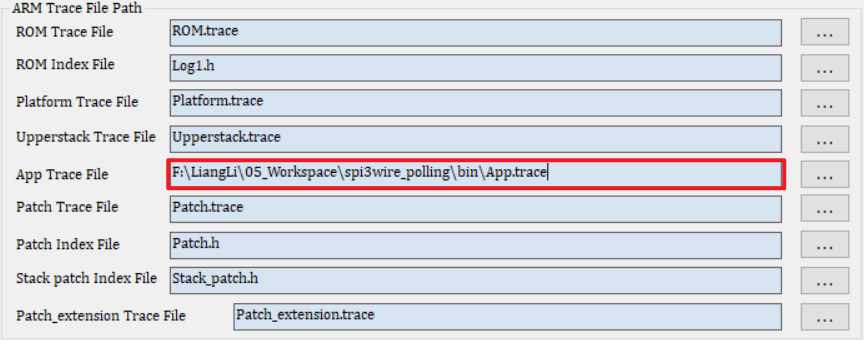

- 需要设置

App Trace File。

- 观察日志输出

COM SETTING

UART SETTING

PERIPHERAL

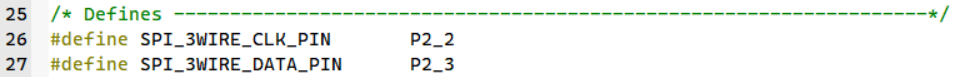

3-WIRED SPI

以下是主控板 RTL8762D 的SDK对3线SPI的相关设置结构体。

1 | typedef struct |

WRITING-DELAY

\[ 1s = 1^3ms = 1^6us = 1^9ns\\ 1Hz = 1^{-3}KHz = 1^{-6}MHz = 1^{-9}GHz \]

在3线SPI的数据线读取过程中,在前一段地址帧结束且尚未开始读取数据前,会有一段延时。由

spiReadDelay 和 spiWireSpeed 两个参数控制。

\[

DelayTime = (spiReadDelay +1) / (2* spiWireSpeed)

\tag{延时计算公式}

\] 例如, 当 spiWireSpeed = 8e5 时, 设置

spiReadDelay = 0x03 ,此时 可以在中间延时

2.5us 。

CLOCK_FREQ

将RTL8762D的SPI通信时钟频率从 2E7 更改为

1E6

后可以短时间正常通信,但是稍微过一段时间就出现了不稳定,度数全为

0 ,且复位后读取的 chipID 也为

0x00, 0x00 。

1 | // the actual frequency of spi is set by `SPI3_WIRE_SysClock` |

TIMING

\[ Sysclk = 1e7 \\ wirespeek = 8e5 \]

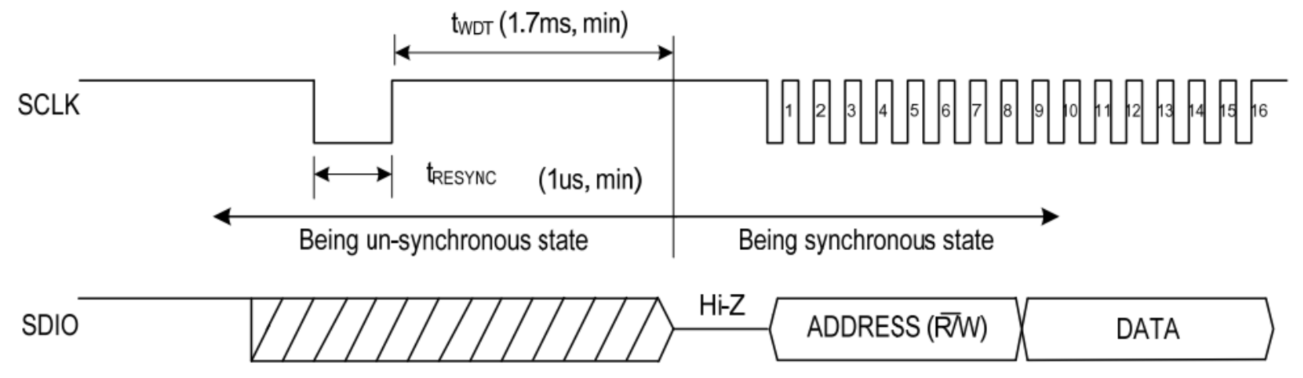

2-WIRED SPI

To recover the correct communication of SPI, the host controller can de-assert the SCLK for at least tRESYNC (1us min), and then keep SCLK asserted for a certain time interval tWDT (1.7ms, min) as shown in below Figure . to force the SPI control circuits of the sensor to reset.

DEBUG RECORDS

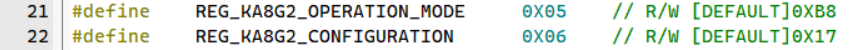

0x05 // 0000 0101

// 1000 0101

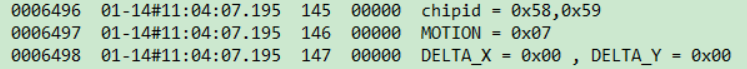

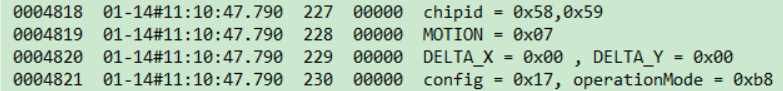

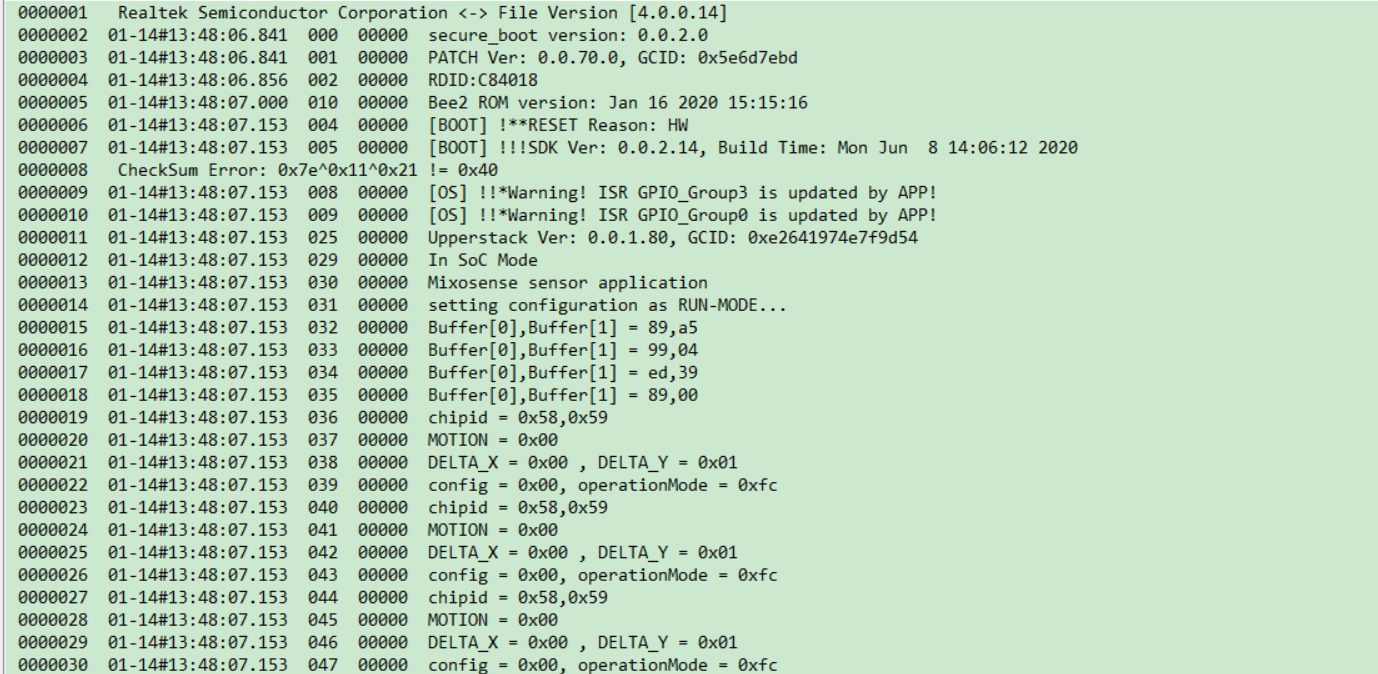

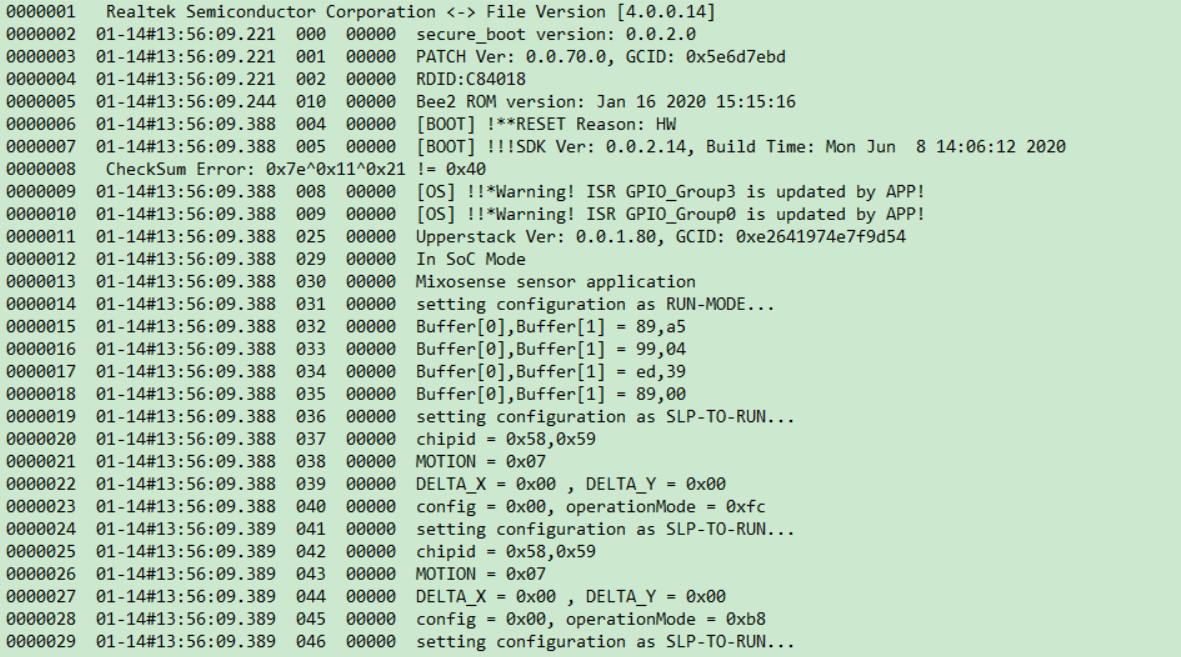

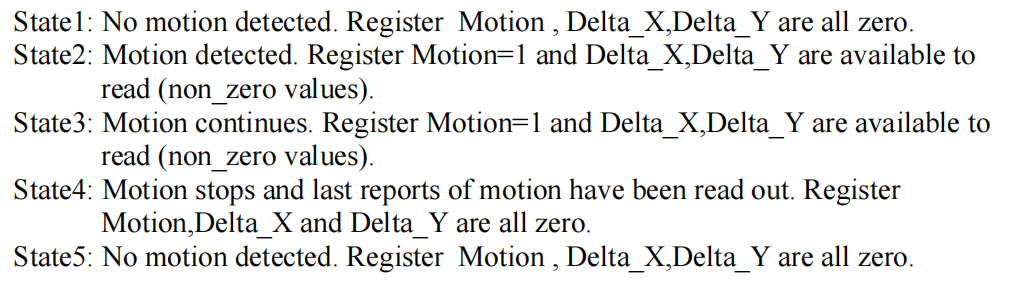

DELTA_X & DELTA_Y UNREAD

Motion DYOVF DXOVF

并未读出,未检测到移动。

Operation_Mode = 0xB8, cofiguration = 0x17 均为默认

0xB8 使

设备处于睡眠模式,configuration = 0x17 使设备未处于

sleep3 且 powerDown 为正常模式,即未断电。

所以需要修改 Operation_Mode 为 0x01 。

在设置了下方的语句之后,LOG记录传送回来的 OperationMode

对应的数据为 0xFC 或 0xB8 (

1111 1100 和 1011 1000) 。

默认情况下 OperationMode 为 0xB8 即

1011 1000 。

异常情况下 OperationMode 为 0xFC 即

1111 1100 。

即第 2 位和 第 6

位会变,查数据手册,只有第 2

位(Slp2mu_Enh)有影响,该位控制芯片强制进入

睡眠2 模式。

1 | spi3wire_writebyte(REG_KA8G2_OPERATION_MODE, KA8G2_OM_RUN); // edited by liew in 20211114 |

从《KA8G2 optical mouse sensor》中的 MOTION Pin

Function 可以看出,Motion

寄存器即运动检测标志相关寄存器。

主控板IO口数据异常

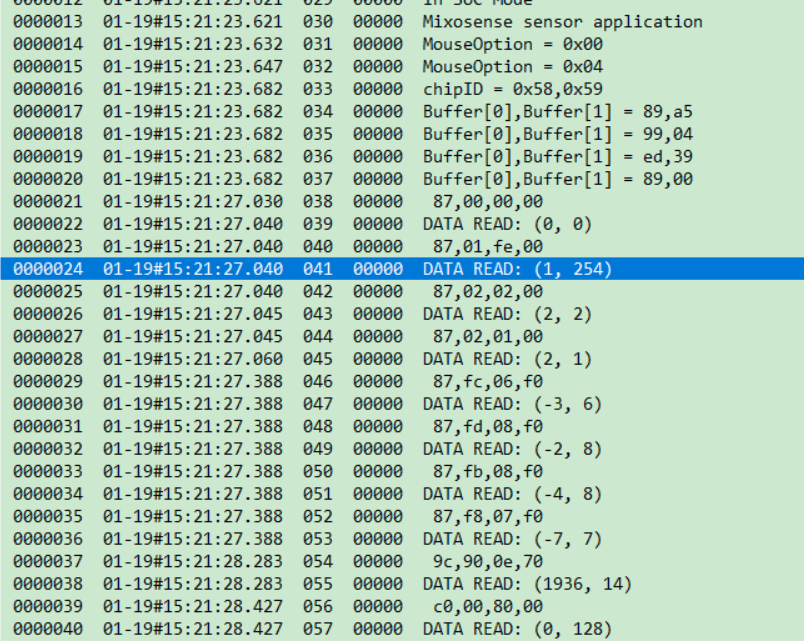

下方为利用SDK进行 读数据 的相关操作:

1 | int main(void){ |

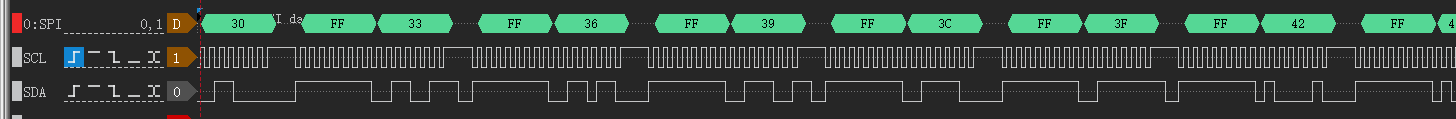

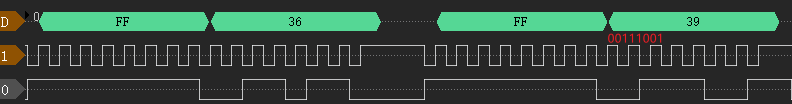

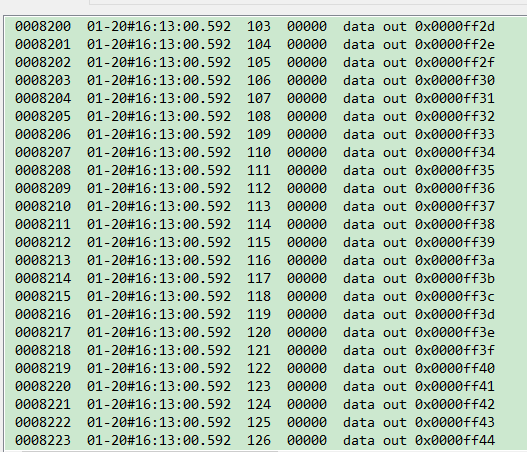

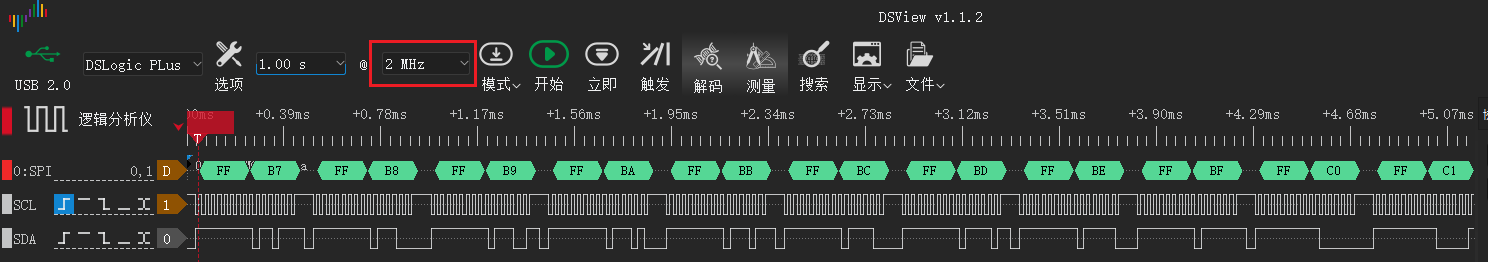

并用逻辑分析仪进行捕获和分析,发现数据异常:

经过检查,发现时序解码无误,所有波形的高低和解码结果一致。

但是相连的数据之间数据差异较大。

查看LOG也发现数据的确有按照预定的逻辑进行循环:

但是逻辑分析仪采出来的数据就是异常。

经过分析,是因为逻辑分析仪的采样率为 1MHz

,与SPI外设的频率 1e6 一致。

修改了逻辑分析仪的采样率为 2MHz

,提高了1倍,采样出来的逻辑就正常了。

但是之前的项目只用了写数据的函数。示波器波形和逻辑分析仪都能正常。

改了项目主循环中的语句为读数据之后,就出现异常了。

问题推断

通过注释部分语句,进行间歇性测试和波形观察。

发现,spi读取语句

uint8_t spi3wire_readbyte(uint8_t address)

可能是波形不正常的原因。

硬件查找主控板和底板的引脚问题:

- 找到扩展板上的GPIO口对应核心板上的哪个口

- 使用示波器探头直接接触对应的GPIO口并查看波形,查看主控板和底板之间是否存在问题。

发现示波器探头从底板更换至主控板之后,示波器所显示波形并无差异。