嵌入式芯片外设

嵌入式芯片(如MCU、DSP等)内部包含众多的模块化外设,如 串口控制模块,SPI模块,I2C模块,A/D模块,PWM模块,CAN模块,EEPROM,比较器模块,等等,它们都集成在芯片内部,有相对应的内部控制寄存器,可通过指令直接控制。

按照控制信号类别对外设进行分类,可以分为 模拟外设(Analog Peripherals)、控制外设(Control Peripherals) 和 通信外设(Communication Peripherals)。

模拟外设 的常见外设如 模数转换器(Analog-to-Digital Convertor, ADC)、可编程增益放大器(Programmable Gain Amplifier, PGA)、温度传感器(Temperature Sensor)、缓冲数模转换器(Buffered Digital-to-Analog Convertor, DAC)和 比较器(Comparator Subsystem)。

控制外设 的常见设备如 捕获器(Capture, CAP)、脉冲幅频调制器(Pulse Width Modulator, PWM)、正交编码器脉冲( Quadrature Encoder Pulse, QEP)和 西格玛-德尔塔滤波器模块 (Sigma-Delta Filter Module, SDFM)。

通信外设 的常见设备如 (Controller Area Network, CAN)、双线通信(Inter-Integrated Circuit, I2C)、电源管理总线接口(Power Management Bus Interface, PMBus)、串行通信接口(Serial Communications Interface, SCI)、串行外设接口(Serial Peripheral Interface, SPI)、局域互联网络(Local Interconnect Network, LIN) 和 高速串行接口(Fast Serial Interface, FSI)。

CLA

为了解决DSP在对实时控制要求比较高的场合中CPU计算速度不足以及计算负担过重,TI很早之前就已经推出了具有CLA功能的DSP。

CLA,即Control Law Accelerator,是一个32位浮点数计算加速器,可以理解为一个专门为浮点数运算而优化的CPU。其可以 独立 于CPU进行运算操作,并 可以同时访问 到ePWM,eCAP,eQEP,ADC result以及Comparator 寄存器。相当于两个CPU并行工作,从而减少了主CPU的运算负担。

也就是说 CLA可以同时访问所有模拟外设的寄存器。

可以将CLA看作是辅助CPU进行计算的浮点运算协处理器(co-processor)。

一个典型的应用场景如下:

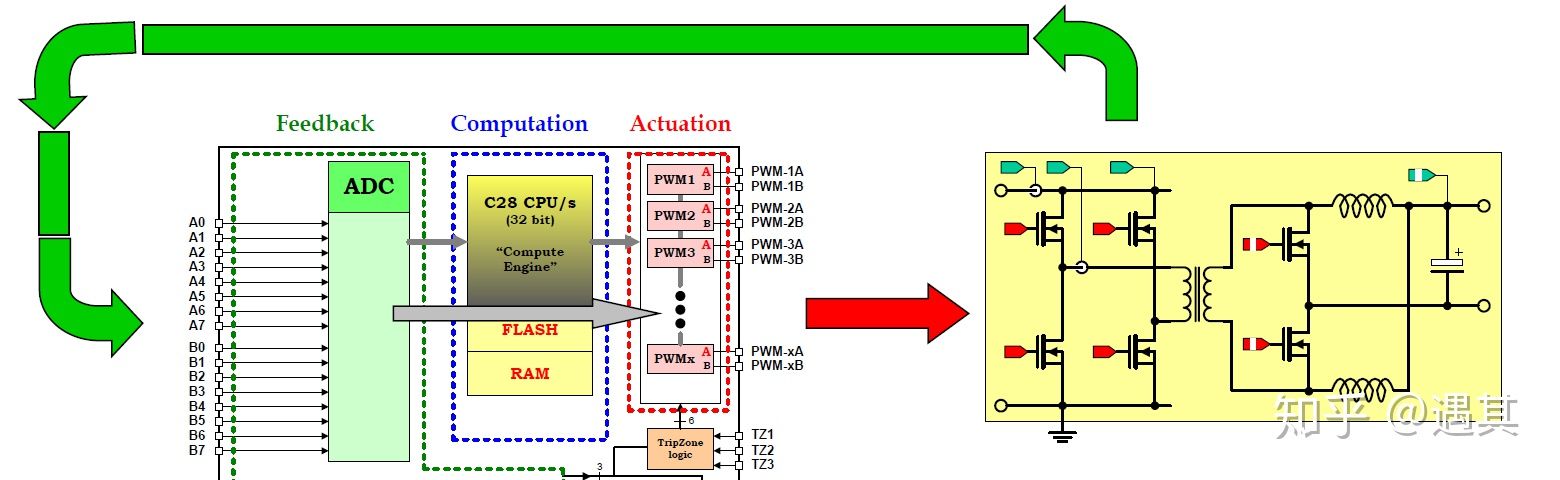

闭环控制电路

闭环控制电路

CPU通过ADC采集主电路的电压、电流信息,计算得到控制逻辑(包括频率以及占空比等),从而控制电路工作。因此如果CPU的计算负担很大,比如说需要计算傅里叶分解,比如说需要计算反三角函数等,那么就造成了极大的控制时延。而CLA应运而生,专门为计算浮点数进行优化,且不会造成CPU阻塞于计算而对异常情况无法响应的情况。

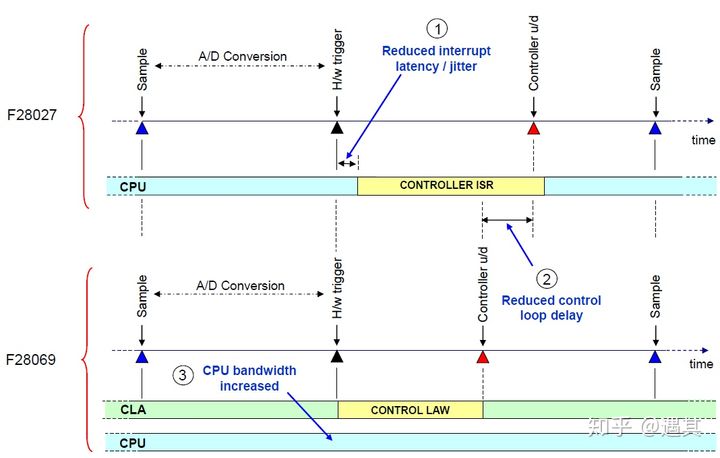

上图则对比了具有CLA功能的28069和不具有CLA功能的28027的控制延时。对于没有CLA功能的28027,其CPU在ADC采样结束之后触发SOC中断,随后进行闭环计算,最后再结束一个周期的控制,开始下一个周期。而具有CLA功能的28069则可以在采样结束之后立即自主触发CLA计算(由于没有菊花链,所以触发迅速),并且由于CLA针对浮点数计算进行优化,因此计算时间更短。更重要的是,CPU不需要进行任何操作,因此CPU可以有空闲完成其他任务,比如异常检测,比如故障上报等等。

简单来说,采用CLA的系统具有更小的计算时延,CPU负担更小,因此其系统更加迅速稳定。

CLB

The C2000 configurable logic block (CLB) is a collection of configurable blocks that interconnect through software to implement custom digital logic functions.

The CLB subsystem contains a number of identical tiles.

GPIO

GPIO,即General-purpose input/output,通用型之输入输出(接口)。功能类似8051的P0—P3,其接脚可以供使用者由程控自由使用,PIN脚依现实考量可作为通用输入(GPI)或通用输出(GPO)或通用输入与输出(GPIO),如当clk generator, chip select等。 既然一个引脚可以用于输入、输出或其他特殊功能,那么一定有寄存器用来选择这些功能。对于输入,一定可以通过读取某个寄存器来确定引脚电位的高低;对于输出,一定可以通过写入某个寄存器来让这个引脚输出高电位或者低电位;对于其他特殊功能,则有另外的寄存器来控制它们。

CMPSS

CMPSS,即Comparator Subsystem,比较器子系统。由模拟比较器和支持电路组成,可用于峰值电流模式控制、开关电源、功率因数校正、电压跳闸监测等应用。

每个CMPSS包含两个比较器、两个12位DAC参考、两个数字滤波器和一个斜坡发生器。比较器在每个模块中表示为“H”或“L”,其中“H”和“L”分别表示高和低。每个比较器产生一个数字输出,指示正输入端的电压是否大于负输入端的电压。比较器的正输入由外部引脚或PGA驱动,负输入可由外部引脚或可编程参考12位DAC驱动。每个比较器输出通过一个可编程的数字滤波器,可以消除假跳闸信号。如果不需要滤波,也可以使用未滤波的输出。一个可选的斜坡发生器电路可用于控制高比较器的12位参考DAC值。

CAN

A controller area network(CAN) is ideally suited to the many high-level industrial protocols embracing CAN and ISO-11898:2003 as their physical layer.

Introduction

The CAN bus was developed by BOSCH as a multi-master, message broadcast system that specifies a maximum signaling rate of 1 megabit per second(bps).

CAN is an International Standardization Organization (ISO) defined serial communications bus originally developed for the automotive industry to replace the complex wiring harness with a two-wire bus.

CAN does not send large blocks of data point-to-point from node A to Node B under the supervision of the central bus master.

In a CAN network, many short messages like temperature or RPM are broadcast to the entire network, which provides for data consistency in every node of the system. 保证系统中各节点的数据一致性。

CAN's specification calls for high immunity to electrical interface and the ability to self-diagnose and repair data errors.

以下为ISO 11898 对 CAN 标准架构层级解释框图:

The CAN communication protocol is a carrier-sense, multiple-access protocol with collision detection and arbitration on message priority (CSMA / CD+AMP). CSMA means that each node on a bus must wait for a prescribed period of inactivity before attempting to send a message. CD+AMP means that collisions are resolved through a bit-wise arbitration, based on a preprogrammed priority of each message in the identifier field of a message. The higher priority identifier always wins bus access.

CAN 包含 standard CAN 和 Extended CAN。

术语

菊花链:在电子电气工程中菊花链代表一种配线方案,例如设备A和设备B用电缆相连,设备B再用电缆和设备C相连,设备C用电缆和设备D相连,在这种连接方法中不会形成网状的拓扑结构,只有相邻的设备之间才能直接通信,例如在上例中设备A是不能和设备C直接通信的,它们必须通过设备B来中转,这种方法同样不会形成环路。因为最后一个设备不会连向第一个设备。这种连线方法能够用来传输电力,数字信号和模拟信号。