I2C通信

I2C基本通信规则

标准:《NXP_UM10204_I2C-bus specification and user manual》

IIC总线是一个事实上的世界标准,现在已经在50多家公司生产的1000多种不同的IC中实施。

此外,多功能的IIC总线被用于各种控制架构,如系统管理总线(SMBus)、电源管理总线(PMBus)、智能平台管理接口(IPMI)、显示数据通道(DDC)和高级电信计算架构(ATCA)。

本文件帮助设备和系统设计者了解IIC总线的工作原理并实现工作应用。描述了各种操作模式。它包含了对IIC总线数据传输、握手和总线仲裁方案的全面介绍。详细的章节涵盖了IIC总线在每种工作模式下的时序和电气规范。

IIC兼容芯片的设计者应将该文件作为参考,并确保新设备满足该文件中规定的所有限制。包含IIC器件的系统的设计者应审查本文件,并参考各个组件的数据表。

——翻译自标准文件

IIC(Inter-Integrated Circuit)是一种通用的总线协议。它是由Philips(飞利浦)公司,现NXP(恩智浦)半导体开发的一种简单的双向两线制总线协议标准。

对于硬件设计人员来说,只需要2个管脚,极少的连接线和面积,就可以实现芯片间的通讯,对于软件开发者来说,可以使用同一个IIC驱动库,来实现实现不同器件的驱动,大大减少了软件的开发时间。极低的工作电流,降低了系统的功耗,完善的应答机制大大增强通讯的可靠性。

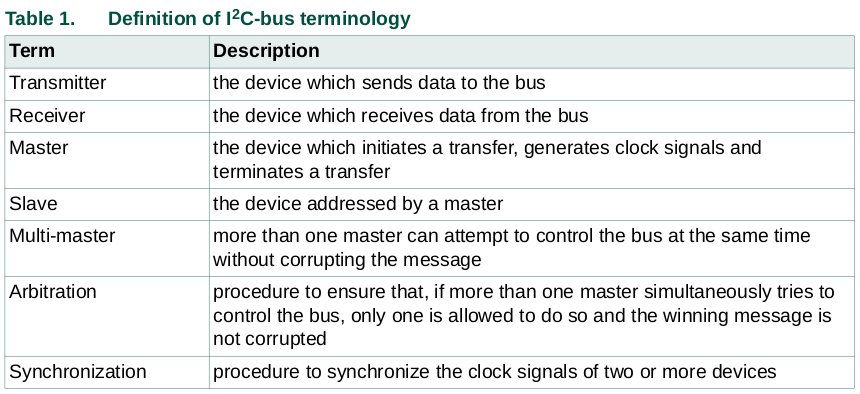

术语

| 术语 | 释义 |

|---|---|

| 总线 | 传输数据的通路 |

| 传送者 | 传输数据至总线的设备 |

| 接收者 | 从总线上接受数据的设备 |

| 主(机) | 主动开启传输、生成时钟信号 并 主动结束传输的设备 |

| 从(机) | 由主机寻址的设备 |

| 多主(机) | 在不损坏数据传输的情况下允许多主机可以试图同时控制总线 |

| 仲裁 | 确保在有多个主机同时试图控制总线的情况下,只允许一个主机这样做,而且仲裁成功的信息不会被(其他设备)破坏的程序。 |

| 同步 | 确保两个及以上设备其时钟信号的同步 |

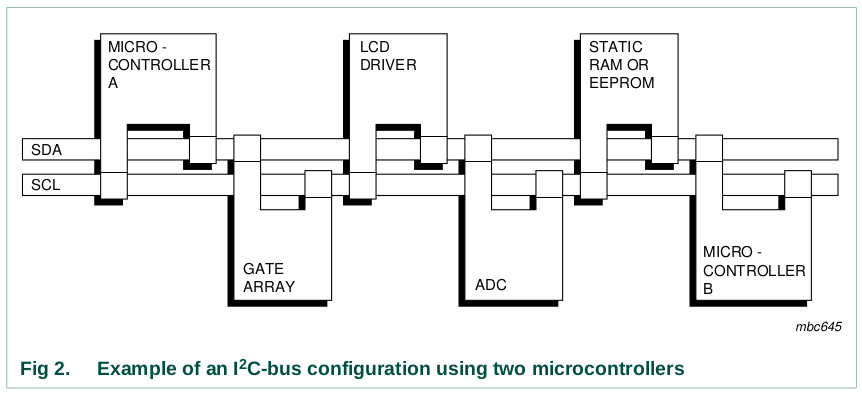

以下这个图应该可以较好地解释“多主机”的概念,多个主机可以同时向外发出传输数据的申请,也可以主动结束其数据传输。虽然,IIC降低了总线复用的成本,但仍需要“仲裁”机制来解决多个主机之间的无序竞争状态。

硬件要求

电气特性

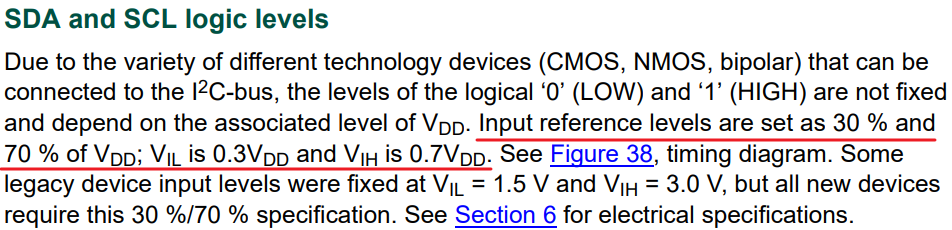

根据要求,I2C的高电平有效值要达到输入参考电压(一般是VDD)的0.7倍以上,低电平有效值需要达到输入参考电压的0.3倍以下。

总线硬件要求

通过 串行数据(SDA,Serial Data)和 串行时钟(SCL,Serial Clock)两条线路对设备进行连接。

每个设备都通过自身的通信设备地址进行互相辨别,且每个设备都可以当发送者或接收者,取决于设备自身的功能定义。

标准传输速率

各模式、速率及其传输方向见下方表格。

Data on the IIC-bus can be transferred at rates of up to 100 kbit/s in the Standard-mode, up to 400 kbit/s in the Fast-mode, up to 1 Mbit/s in Fast-mode Plus, or up to 3.4 Mbit/s in the High-speed mode.

| MODE | RATE | TRANSFER DIRECTION | DOWNWARD COMPATIBLE WITH |

|---|---|---|---|

| STANDARD | 100 Kbit/s | bidirectional | / |

| FAST | 400 Kbit/s | bidirectional | STANDARD |

| FAST-PLUS | 1 Mbit/s | bidirectional | STANDARD / FAST |

| HIGH-SPEED | 3.4 Mbit/s | bidirectional | STANDARD / FAST / FAST-PLUS |

| ULTRA-FAST | 5 Mbit/s | unidirectional | / |

编码协议

以下协议要求适用于双向通信模式(不包括ULTRA-FAST模式下的单向通信)

逻辑电平规定

由于IIC的接入设备众多(如CMOS、NMOS、Bipolar等),因此逻辑电平0和逻辑电平1(的电压)并不是固定不变的,这取决于VDD的电平。

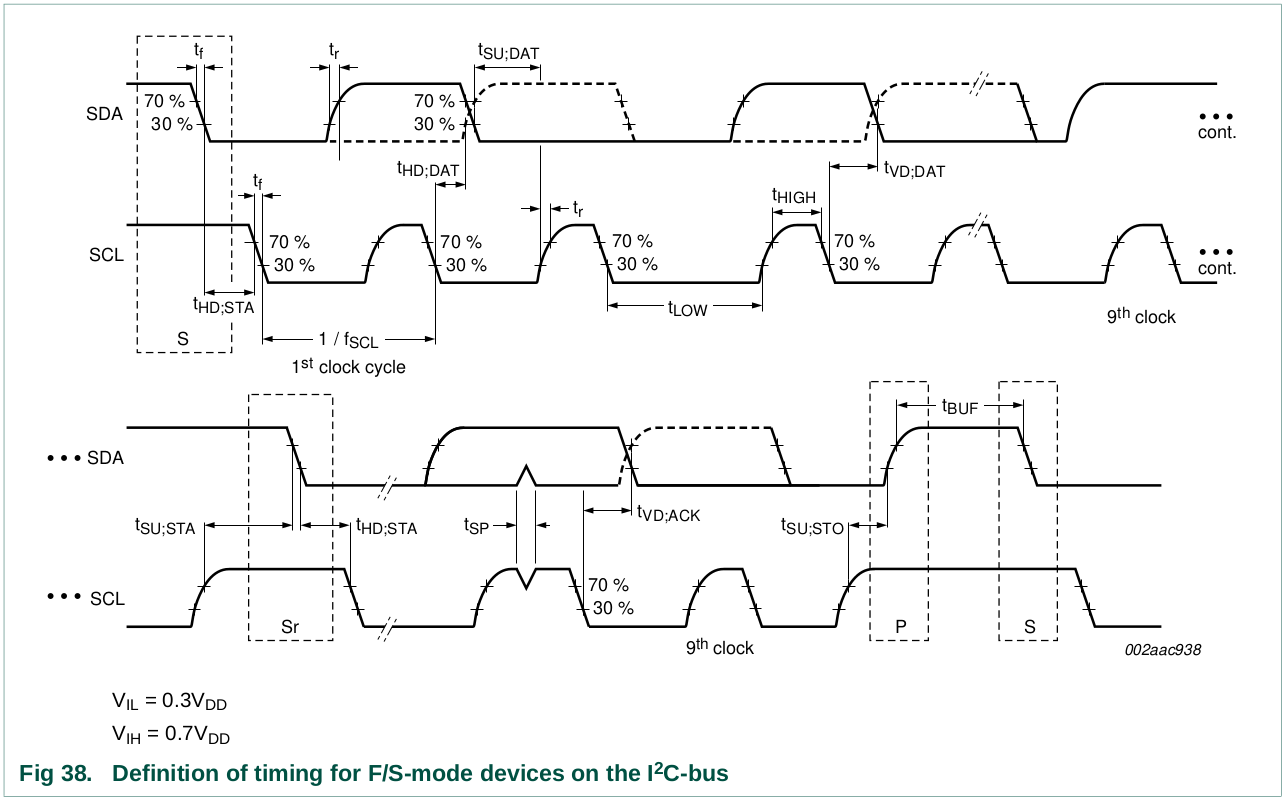

输入参考电平会被控制在VDD电平的30%~70%之间。 VIL = 0.3 * VDD;VIH = 0.7 * VDD 。

某些传统设备的输入电平会被固定在1.5V(VIL)和3.0V(VIH),但新设备都要求是 30%VDD 及 70%VDD 。

注意:VIL、VIH、VOL、VOH都是以参考电压作为基准的,即要达到某个电压的百分之多少时,才能够被认为是 逻辑电平0 或 逻辑电平1 。例如,可将VIL 视作当VDD下降到只有30%及以下时,为逻辑电平0,30%VDD是其逻辑电平的最高阈值;同理可得 VIH ;超过这个值而未到达70%的中间态则为不确定态。

Due to the variety of different technology devices (CMOS, NMOS, bipolar) that can be connected to the IIC-bus, the levels of the logical ‘0’ (LOW) and ‘1’ (HIGH) are not fixed and depend on the associated level of VDD . Input reference levels are set as 30 % and 70 % of VDD ; VIL is 0.3VDD and VIH is 0.7V DD .

See Figure 38, timing diagram. Some legacy device input levels were fixed at VIL = 1.5 V and VIH = 3.0 V, but all new devices require this 30 %/70 % specification.

时序正确性

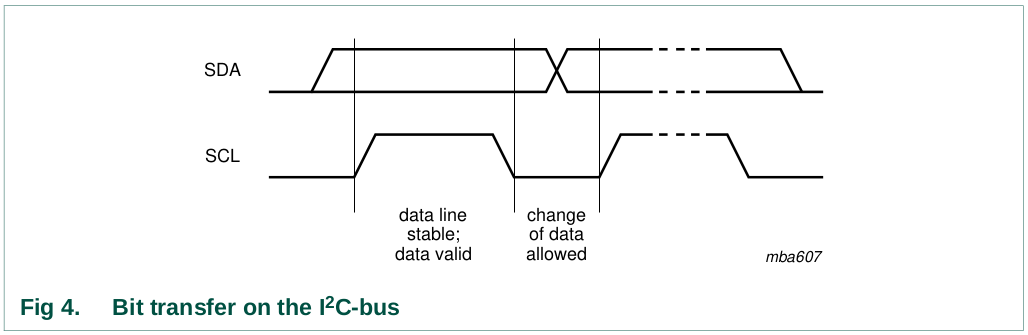

- SDA上的数据必须在SCL高电平期间保持稳定,即不能在SCL高电平期间发生翻转(后见原因),只有在SCL低电平时可以翻转。

- 时钟脉冲信号生成要先于数据传送。

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (see Figure 4). One clock pulse is generated for each data bit transferred.

开始及结束标志

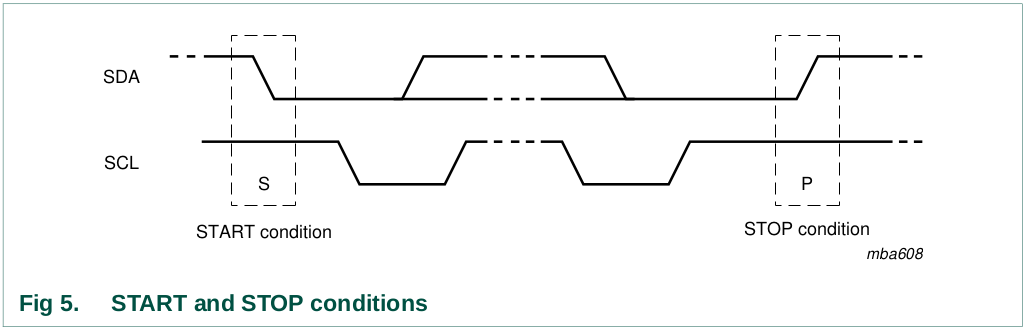

传输开始时必须以一个 开始 信号作为标志,结束时必须以一个 结束 信号作为标志。

开始信号 是以SCL为高电平时的 SDA电平的由高转低 作为标志,结束信号 是以SCL高电平时的 SDA电平的由低转高 作为标志。

开始和结束标志必须由主设备控制。

All transactions begin with a START (S) and are terminated by a STOP (P) (see Figure 5). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

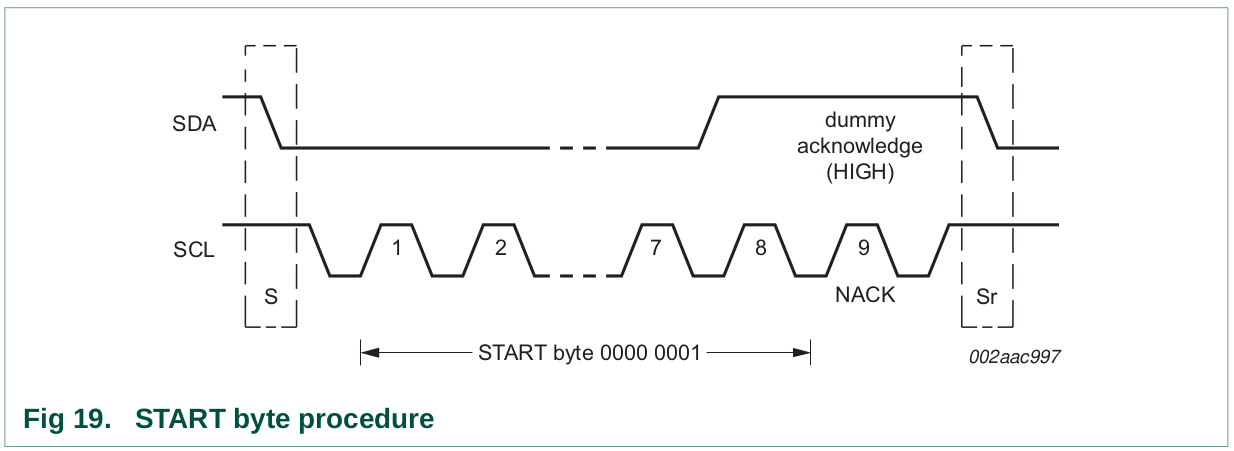

开始字节

dummy acknowledge (HIGH) : 无声确认???

总线状态

总线具有两种状态,繁忙(Busy)和 空闲(Free),即 SDA电平 “开始” 后,总线进入繁忙状态, SDA电平 “结束” 后,总线进入空闲状态。

注意:在总线繁忙期间,发生重复的“开始”状态(而不是“结束”状态),由于“重复开始”和 “开始” 功能相同,为了方便,统称为 “开始”,除非特殊说明为 “重复开始”。

The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical. For the remainder of this document, therefore, the S symbol is used as a generic term to represent both the START and repeated START conditions, unless Sr is particularly relevant.

传输比特位

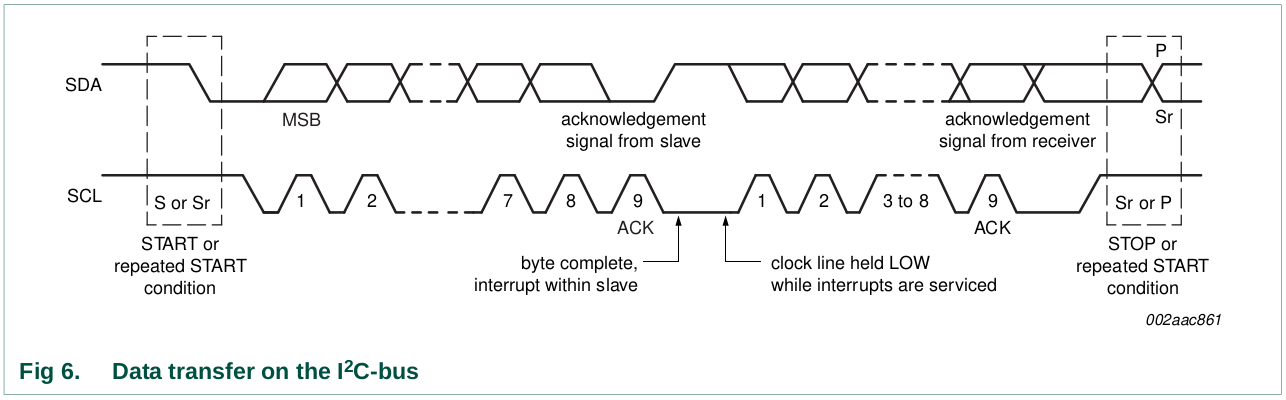

- SDA线上的字节传输必须满足8位长度。

- 每次传输数据的字节数不受限制。

- 每个字节数后都需要跟一个确认位(Acknowledge bit)。

- 当从机无法完整接收或传输一个完整的数据字节时,例如正在产生内部中断等,除非其完成内部的某些功能,否则该从机将能够一直拉低SCL的电平,强制让主机一直处于等待状态。只有当从机准备好接收下一个完整的字节并释放SCL时,数据传输才会继续。

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit.

Data is transferred with the Most Significant Bit (MSB) first (see Figure 6). If a slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

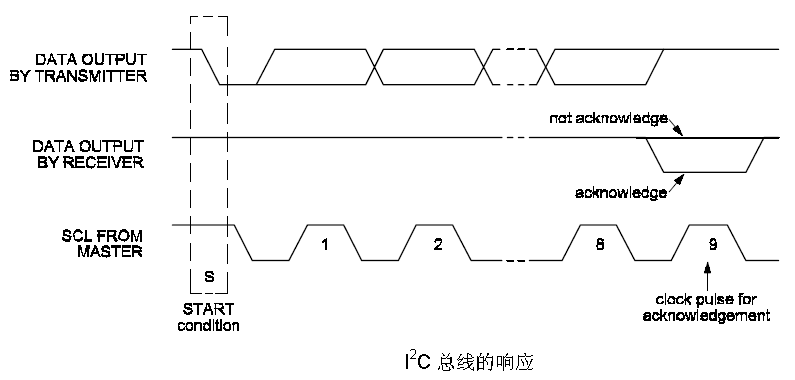

确认标志

- 每个字节(8比特)后都跟着一个确认位,即前8位数据,第9位确认。

- SCL上的时钟信号由主机产生,包括确认位的的第九个时钟脉冲。

- SDA线并不是由主机一直占有的,每发送完一个完整字节后,主机都会释放SDA线,由从机进行数据确认。

- 发送者在确认时钟脉冲期间释放SDA线,以便接收者可以将SDA线拉低,并且在该时钟脉冲的高电平期间保持稳定的低电平。

- 对于设置(set-up)和保持(Hold)的时间,都应该依照表10中只针对各种不同模式的要求进行设置。

- 如果SDA电平在第九个时钟脉冲时仍保持高电平,则被定义为 “未确认状态”。则此时主机可以发送一个“结束”标志来结束当前连接,或发送一个“开始”标志来开启一次新的传送。

即,此时(第9个脉冲时)SDA的控制权已经被mater释放了,但仍为高电平,slave可以在这第9个时钟脉冲高电平期间获得控制权,如果确认收到数据,则将电平拉低,否则不拉低。

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. The master generates all clock pulses, including the acknowledge ninth clock pulse.

The Acknowledge signal is defined as follows: the transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse (see Figure 4). Set-up and hold times (specified in Section 6) must also be taken into account.

When SDA remains HIGH during this ninth clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

以下为五种“未确认/未应答”的可能情况:There are five conditions that lead to the generation of a NACK:

- 传输地址错误:No receiver is present on the bus with the transmitted address so there is no device to respond with an acknowledge.

- 实时处理中:The receiver is unable to receive or transmit because it is performing some real-time function and is not ready to start communication with the master.

- 数据/代码未定义:During the transfer, the receiver gets data or commands that it does not understand.

- 正在传输中:During the transfer, the receiver cannot receive any more data bytes.

- 未收到结束信号(收发身份未转换):A master-receiver must signal the end of the transfer to the slave transmitter.

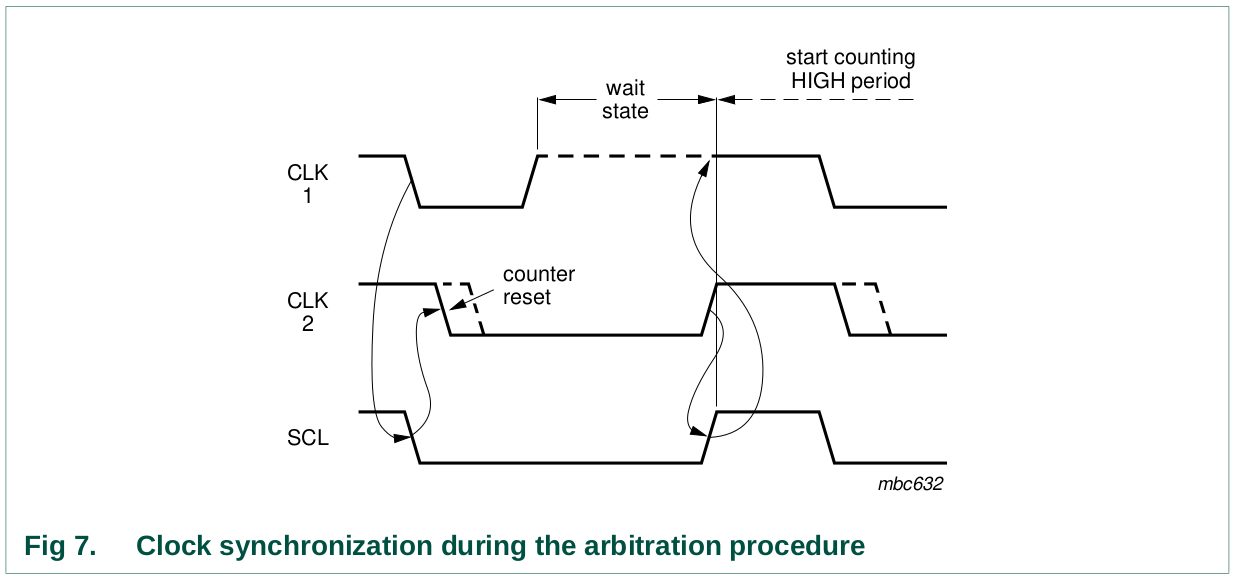

时钟同步

任意几个主机都可能同时发起数据传输请求,此时只有一个主机和一个从机可以掌握总线进行通信,此时需要通过 时间同步 和 仲裁 完成对总线的调配。

在单机系统(Single Master System)中,不需要时钟同步和仲裁。

时钟同步是通过IIC接口与SCL线的有线-AND连接进行的。

这意味着SCL线上的高电平到低电平的转换会导致相关的主站开始对其低电平周期进行计数(如图7的CLK2),一旦一个主站时钟 CLK1 变为低电平,它就会将SCL线电平拉低,并保持在这个状态,直到另一个时钟 CLK2 达到高电平状态。

然而,如果时钟 CLK2 仍在其低电平周期内,CLK1 的低电平到高电平转换可能不会改变SCL线的状态。

因为SCL线被具有最长的低电平周期的主站 CLK2 保持为低电平,而在这段时间内,低电平周期较短的主站 CLK1 进入高电平等待状态。

Clock synchronization is performed using the wired-AND connection of IIC interfaces to the SCL line. This means that a HIGH to LOW transition on the SCL line causes the masters concerned to start counting off their LOW period and, once a master clock has gone LOW, it holds the SCL line in that state until the clock HIGH state is reached (see Figure 7). However, if another clock is still within its LOW period, the LOW to HIGH transition of this clock may not change the state of the SCL line. The SCL line is therefore held LOW by the master with the longest LOW period. Masters with shorter LOW periods enter a HIGH wait-state during this time.

当所有相关的主控器都结束了他们的低电平周期,时钟线被释放并变成高电平。

然后,在主站时钟和SCL线的状态之间没有差异,所有的主站开始计算他们的高电平周期。

第一个完成其高电平周期的主站再次将SCL线拉到低电平。这样,就产生了一个同步的SCL时钟,其低电平周期由具有最长时钟低电平周期的主站决定,其高电平周期由具有最短时钟高电平周期的主站决定。

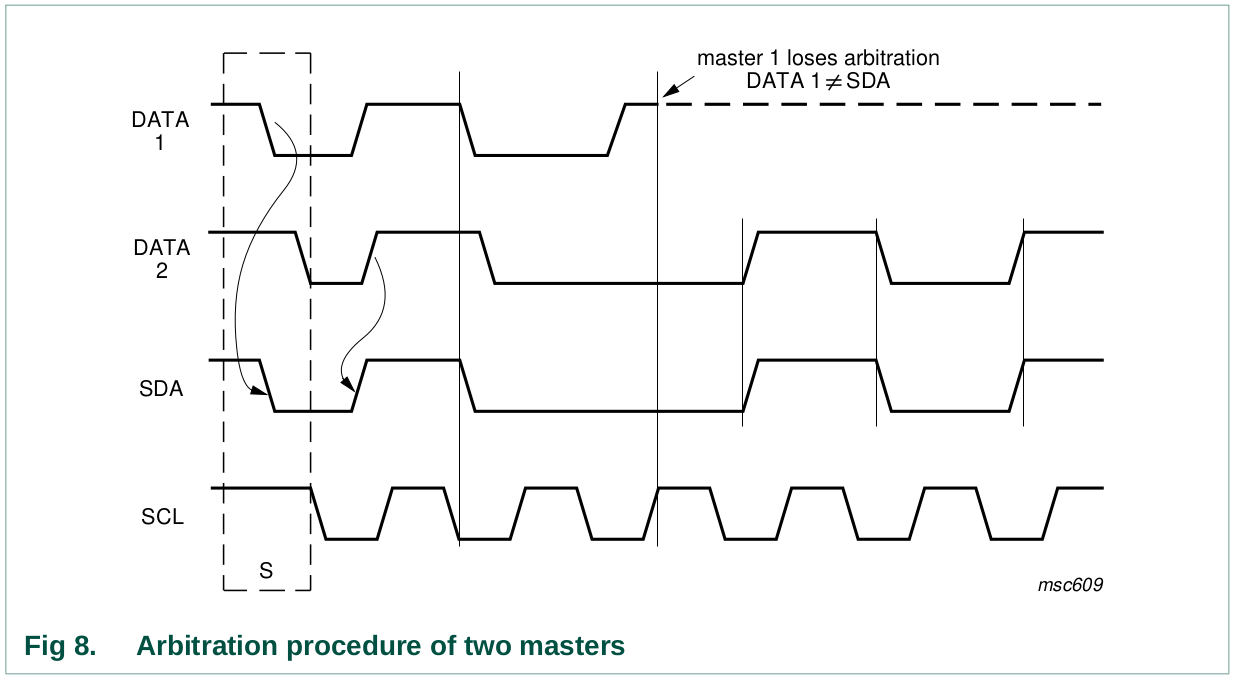

竞争仲裁

仲裁和同步一样,是指只有在系统中使用一个以上的主站时才需要的协议的一个部分。注意,从机不参与仲裁程序。

一个主站只有在总线空闲时才可以开始传输。两个主站可以在START条件的最小保持时间(tHD;STA)内产生一个START条件,从而在总线上产生一个有效的START条件。然后需要进行仲裁,以确定哪个主站将完成其传输。

仲裁是逐位进行的。在每个比特期间,当SCL为高电平时,每个主站检查SDA电平是否与其所发送的内容相符,期间可能需要很多比特,只要传输的内容相同,两个主站实际上可以无误地完成整个信息传输过程。

当一个主站第一次试图发送一个高电平,但检测到SDA电平为低电平时,主站知道它已经失去了仲裁,并关闭其SDA输出驱动器。在其他主站被仲裁过程中,正在传输其信息的主站将继续其传输,没有信息丢失。

失去仲裁的主站可以产生时钟脉冲,直到它失去仲裁的字节结束,并且必须在总线空闲时重新尝试传输。

如果一个主站也包含了一个从站功能,并且它在寻址阶段失去了仲裁,有可能获胜的主站正试图对它进行寻址。因此,失败的主站必须立即切换到其从站模式。

图8显示了两个主站的仲裁程序。可能涉及更多,这取决于有多少个主站连接到总线上。

当产生DATA1的主站的内部数据电平与SDA线上的实际电平有差异时,DATA1的输出被关闭。这并不影响由获胜主站发起的数据传输。

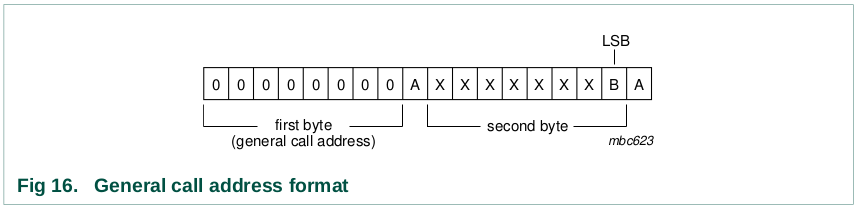

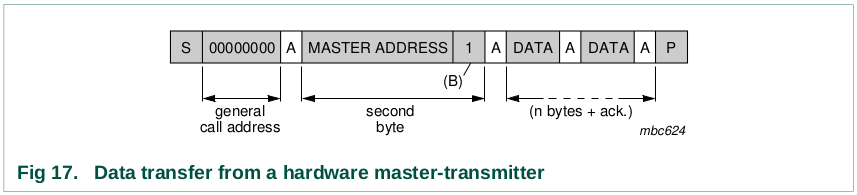

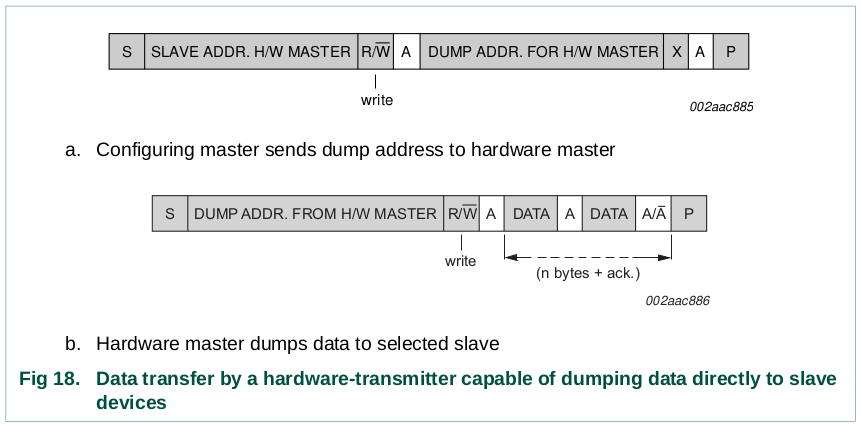

通用寻址

软复位

在发送general call (0000 0000)后,再发送一个 0000 0110 (06h) ,这样两个具有先后顺序的字节来定义软复位。

首先,这种软复位是可选 ,并不是所有设备都会对软复位指令进行响应。

在收到这2个字节的序列时,所有被设计为响应一般调用地址的设备都会复位,并接收其地址的可编程部分。

On receiving this 2-byte sequence, all devices designed to respond to the general call address reset and take in the programmable part of their address.

必须采取预防措施,确保设备在施加电源电压后没有拉低SDA或SCL线,因为这些低电平会阻断总线。

总线复位

SCK信号一直卡在低电平的事件较少发生。

- 如果IIC总线设备拥有硬件复位输入,则可以通过优先程序启用硬件中断复位来重置总线。

- 如果没有硬件复位输入,则通过给设备循环供电,激活强制性的内部开机复位(POR)电路。

SDA信号如果一直卡在低电平。

则主机应该发送九次SCL时钟脉冲,此时令SDA保持低电平的设备在收到九次脉冲后应主动释放总线。

如果九次脉冲没有用,则启用硬件中断复位或循环供电来清除总线。

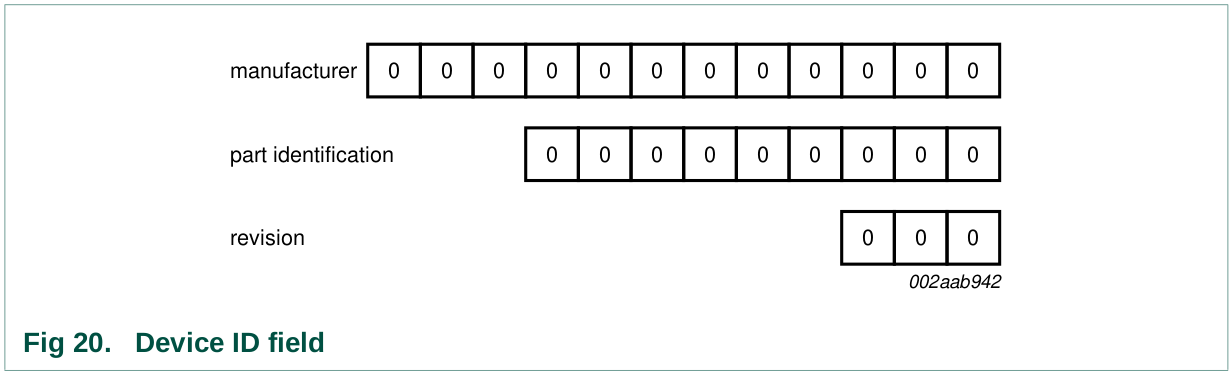

设备ID

可选的3字节只读设备ID编码(an optional 3-byte read-only ):

- 12位是设备制造商编号,具有独一无二性

- 9位零件ID,由设备制造商写入

- 3位模具/晶元版本,由设备制造商写入

启动条件

主站发送保留设备ID的 IIC 总线地址,后面的R/W位设置为

0(写):1111 1000。主站发送从属地址。LSB是一个 "不关心"的值,只有一个设备必须确认这个字节(拥有IIC总线从属地址的设备)。

主站发送一个 Re-START 条件。

备注:在 STOP 条件之后,再加上一个 START 条件,就会重置从属状态机,无法进行设备ID读取。另外,在 STOP 条件或 Re-START 条件之后,对另一个从属设备的访问也会重置从属状态机,无法执行Device ID读取。

主站发送保留设备ID的 IIC 总线地址,后面的R/W位设置为

1(读):1111 1001。可以进行设备ID读取,从12个制造商位开始(第一个字节+第二个字节的4个MSB),然后是9个部件识别位(第二个字节的4个LSB+第三个字节的5个MSB),然后是三个芯片修订位(第三个字节的3个LSB)。

主站通过NACKing最后一个字节来结束读取序列,从而重置从属设备的状态机,允许主站发送 STOP 条件。

备注:设备ID的读取可以随时通过发送NACK来停止。

如果主站在第三个字节之后继续ACK,从站就会滚回第一个字节,并继续发送设备ID序列,直到检测到 NACK。

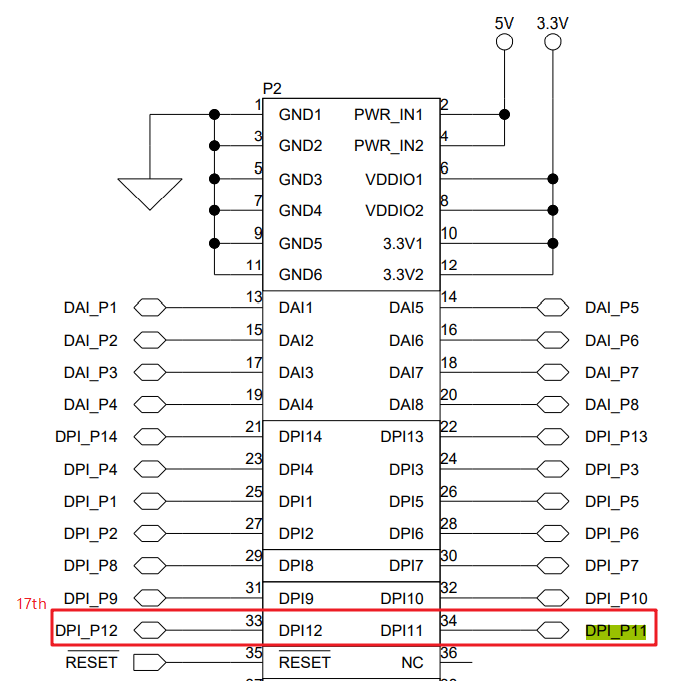

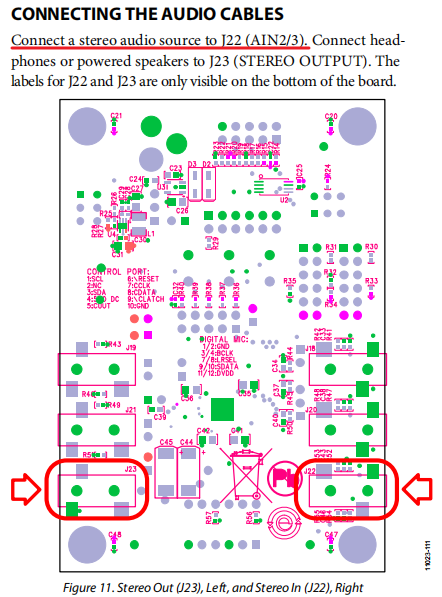

ADI-Codec I2C开发

ADI

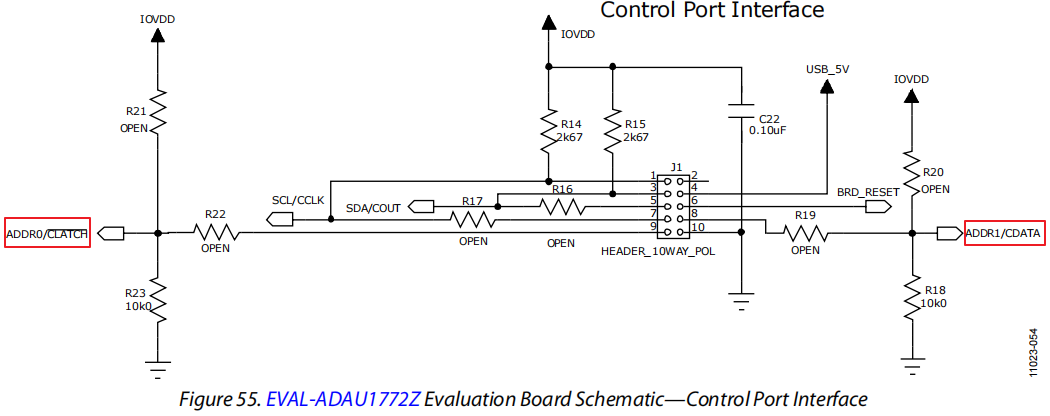

物理接口

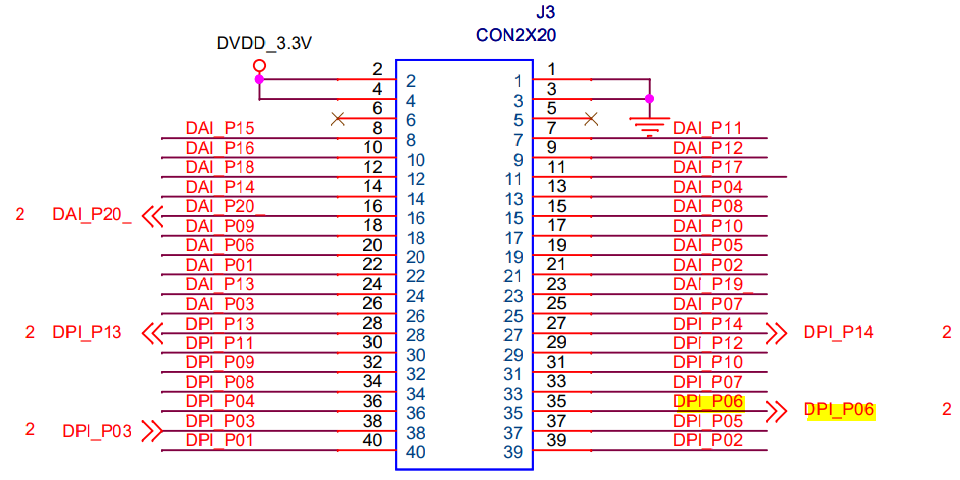

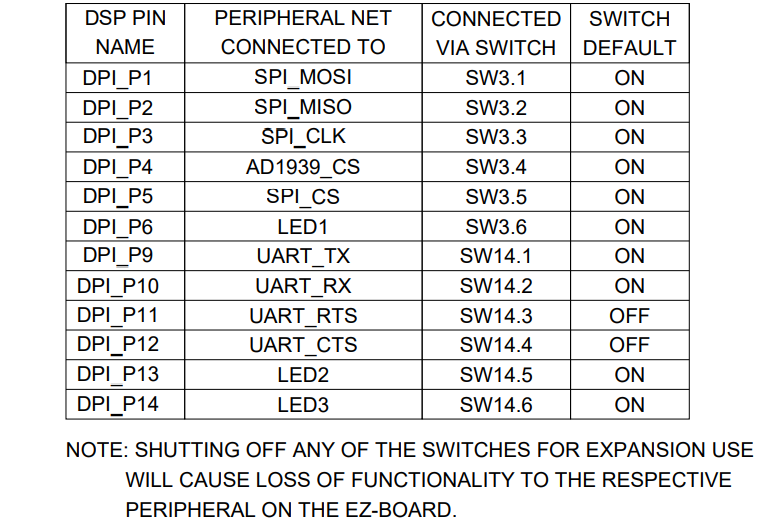

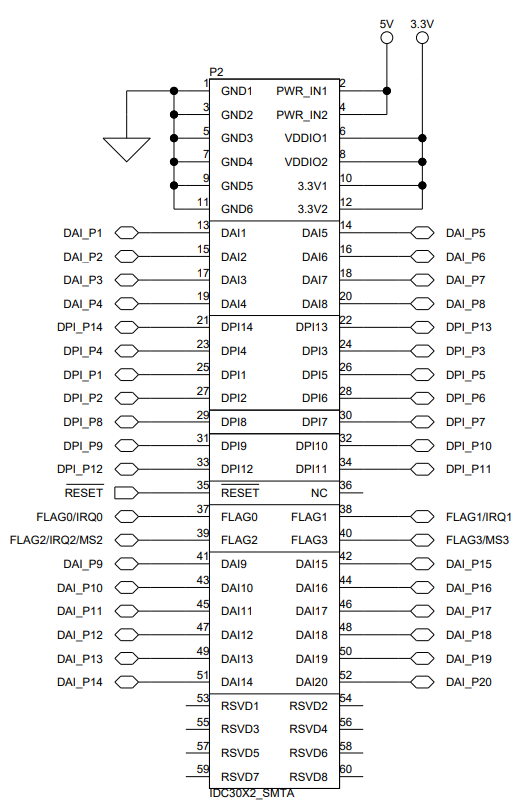

存在由ADI官方提供的评估板(和MediaWorks的板) 和 开发第一板(量产板)之间的引脚定义差别,一开始使用的是评估板的DPI 11 和 12引脚,即 DPI_P11 为 SDA,DPI_P12 为 SCLK。后来发现作为时钟引脚的DPI无法被控制,转而使用 DPI 11 和 13。即 DPI_P11 为 SDA,DPI_P13 为 SCLK。

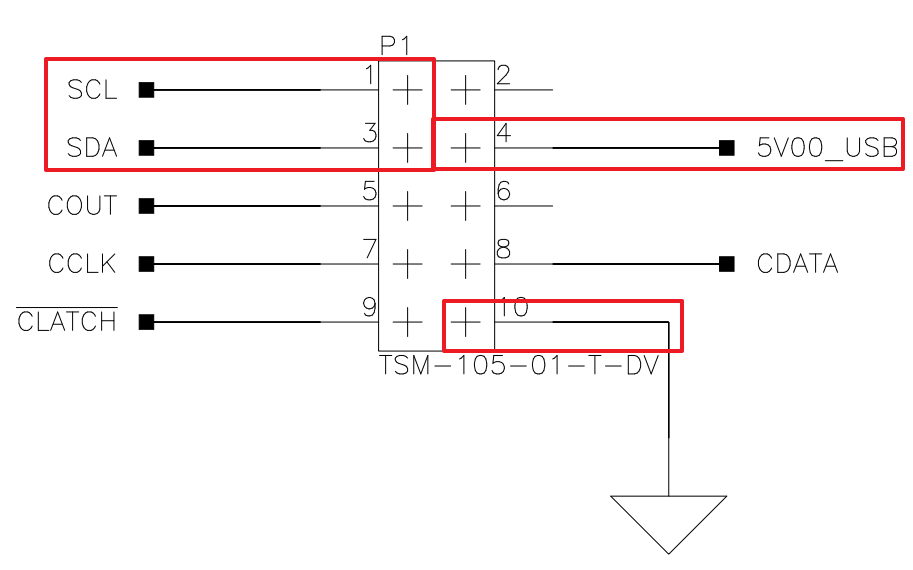

MediaWorks核心板J3引脚排示意图

以下描述均以评估板为例,DIY板不一定适用。

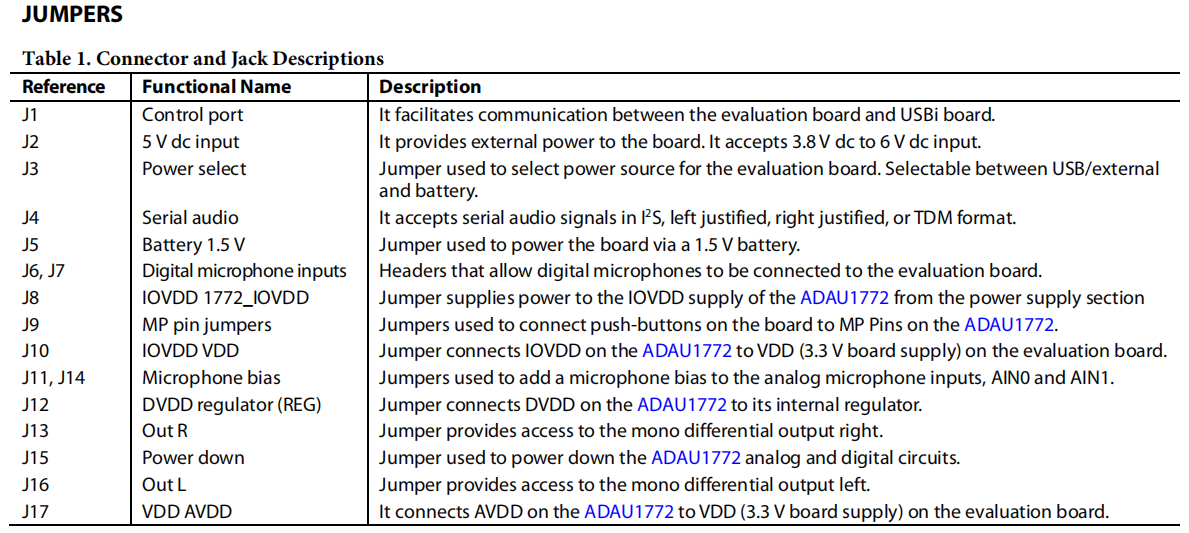

插口(Jumper)定义

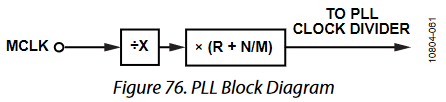

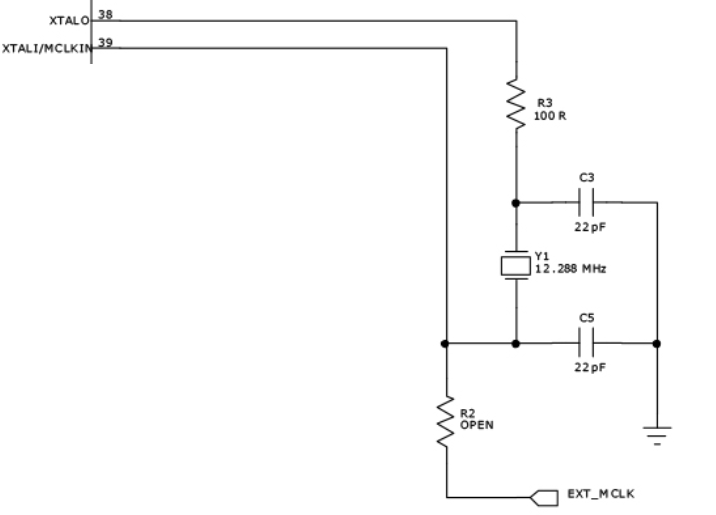

时钟及PLL

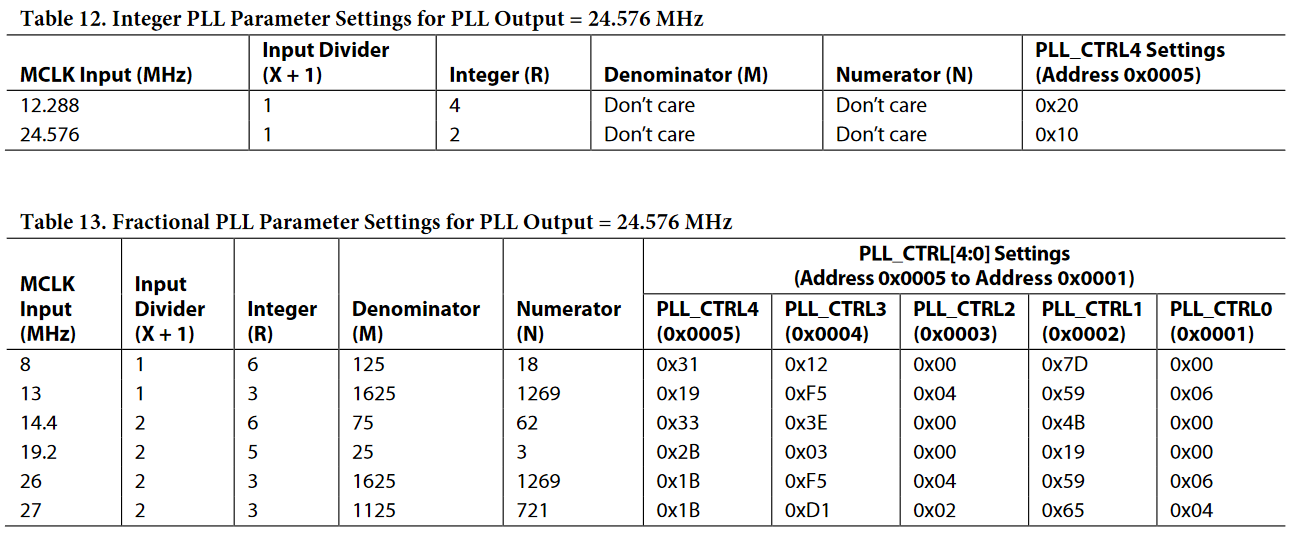

- 1772的工作频率为12.288兆赫,而如果过要设置PLL,PLL输出一定是24.576兆赫。

- 通过

MCLKIN端为codec提供核心时钟信号,可接入8至27兆赫信号。 - 通过对

0x0000到0x0005的寄存器进行写入修改PLL。 - PLL模式要被设置为分数或整数,则取决于MCLK的输入频率。

- 在时钟信号达到PLL前,时钟信号会经过整数时间分频器以确保时钟频率符合要求;可以通过设置 0x0005 的bit[2:1]来设置其分频率。

- 要使用PLL时,首先要明确PLL输出频率是多少,当PLL信号与时钟信号是整数倍关系时才需要使用整数分频器。

以下列举了整数型及分数型分频器的参数设置:

评估板电路图

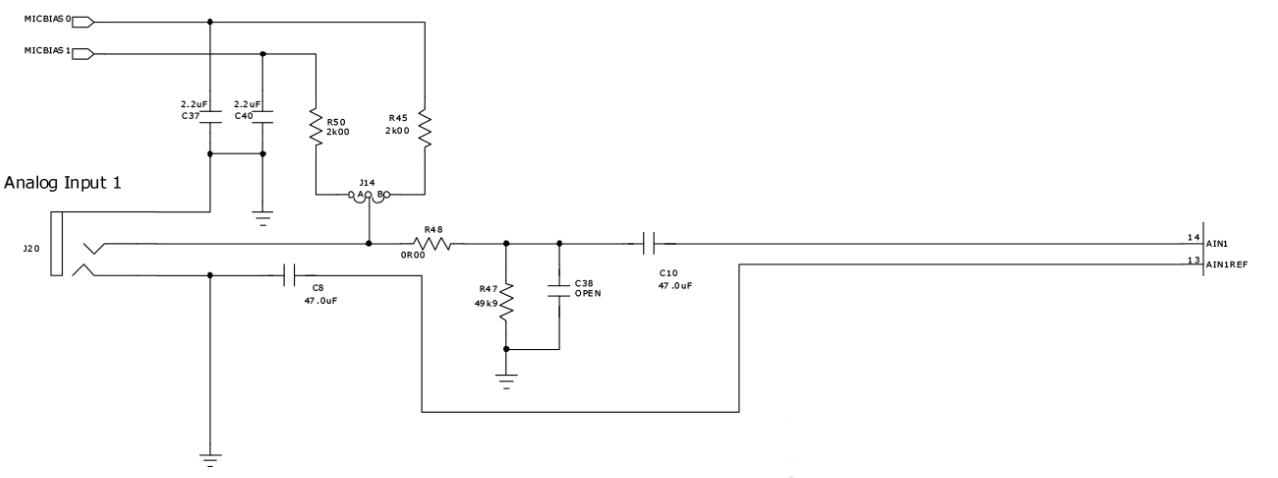

输入输出

评估板电路图

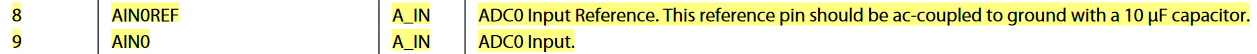

第0及第1通道

以下为codec芯片对引脚的定义,在提供一个接地端,构成TRS是完全没有问题,但是codec的定义和其评估板的外围电路设计有所区别。

正常3.5mm音频接口为TRS接口,其中T虽然为VCC(通常是),R作为音频信号输入,而S为接地端,且T和R可共同作为左右声道分别进行输入。(也有T和S定义相反的设计)

但是按上述电路进行接线时,相当于TS接口(单声道)接线模式,却又不完全相同:

- 使用 MICBIASx 对14接口进行供电,此时Tip端是VCC。

- Ring端接13接口,充当Sleeve端(而实际上的Sleeve端因已经接地,可以不进行连接)。

- 由Ring(AIN1REF)和Tip(AIN1)共同构成了TS单声道接线模式。

第2及第3通道

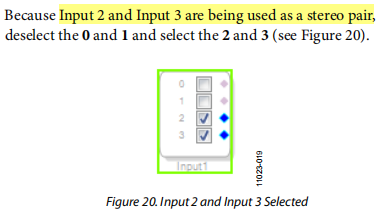

- 2/3输入通道是复用立体声通道,即1通道和0通道都可以单独接入音源,在物理音频接口上独立,但第2/3通道是在一起的,共用一个物理通道。UG第7页中也有提到。

- 有四个单端输入通道可以设置为麦克风信号或线路信号,一个双立体声数字输入信号通道和也可被用于单端输出的两个差分(differential)输出。

I2C通信

时序

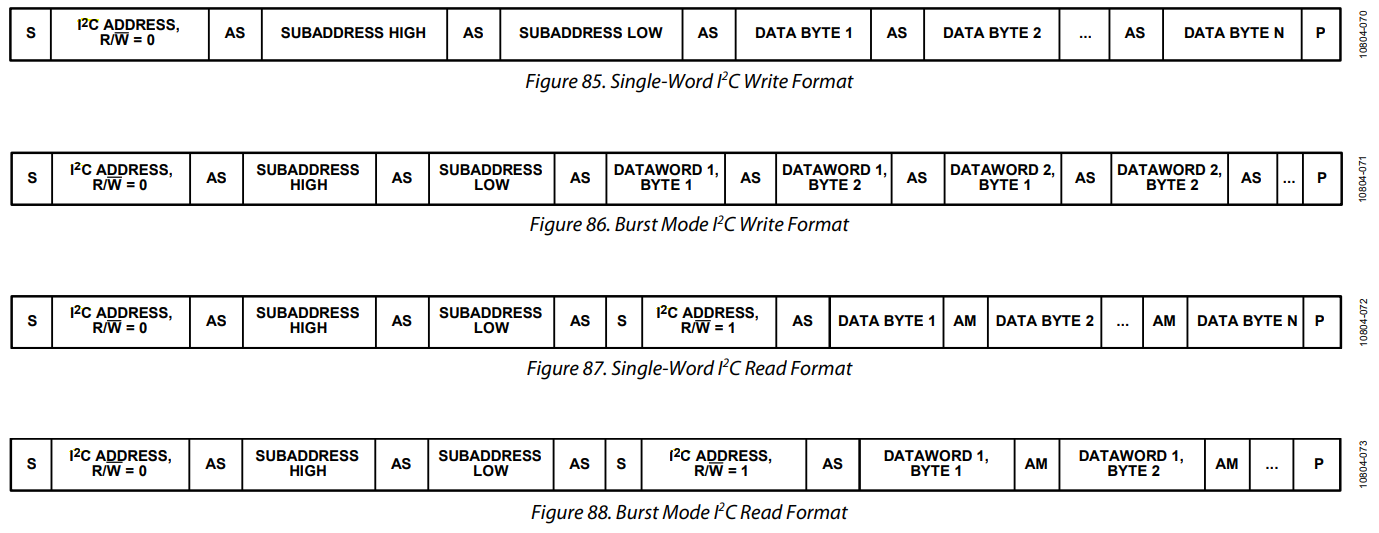

图85展示了 单字主写模式 的时序。每9个时钟脉冲,1772都会拉低一次SDA的电平以表示确认收到。

图86展示了 多字主写模式 的时序。此图展示了2个字节大小数据(例如程序)的写入过程。1772会在每两个字节后增加一次子地址寄存器,因为被使用的子地址对应着 2字节 长度的寄存器或内存区域。

图87展示了 单字主写模式后转变为 单字主读模式 的时序。1772作为从机接受数据后发送确认标志,主机立即发起重复开始的 单字主读模式,由从机发送至主机。

图88展示了 多字主读模式 的时序,展示了读取目标字节为2bytes的示例。此处上述黄底字重复。其他地址范围可能有不同的字长,从一个到四个字节不等。ADAU1772总是对子地址进行解码,并设置自动递增电路,使地址在适当的字节数后递增。

S = 开始 标志

P = 停止 标志

AM = 主机确认标志

AS = 从机确认标志

接口

USBi接口

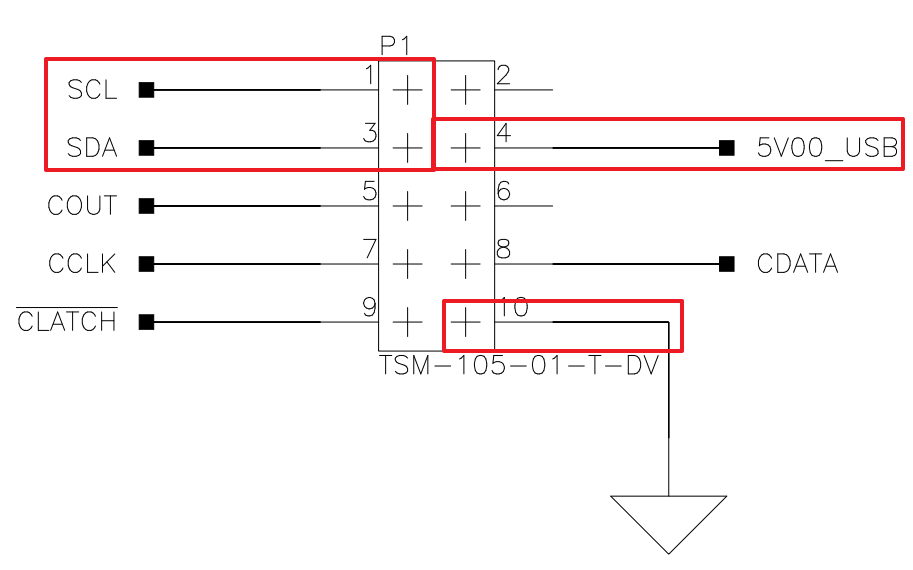

《SigmaStudio_USBi_to_EZ-Board_Adapter_Schematic-Rel_0.1.pdf》中对接口的定义,总共需要4个引脚,分别是1、3、4、10,对应着 SCL / SDA / VCC / GND;

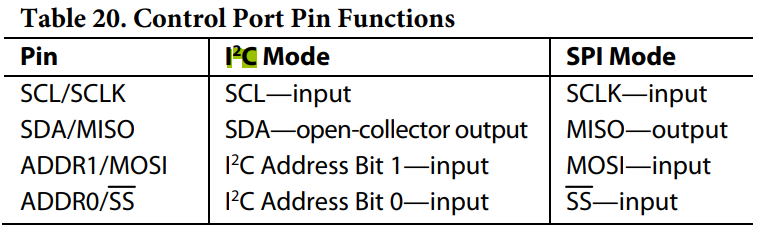

1772接口

需要用到的接口是 SCL/SCLK 和 SDA/MISO

。

ADDR0 和 ADDR1 分别对应的是控制接口(CONTROL PORT)上的 CLATCH 和 CDATA 针脚。

| BIT_6 | BIT_5 | BIT_4 | BIT_3 | BIT_2 | BIT_1 / ADDR1 / CDATA | BIT_0 / ADDR0 / CLATCH | ADDRESS |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0x3C |

| 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0x3D |

| 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0x3E |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0x3F |

21479接口

《ADSP-21479 EZ-Board Evaluation System Manual》,需要用到的接口是

SPI_CLK(DPI_P3) 和 SPI_MISO(DPI_P2) 。

对应评估板上的针脚接口如下图示 24(DPI_P3) 和 27(DPI_P2) 接口。

设备地址

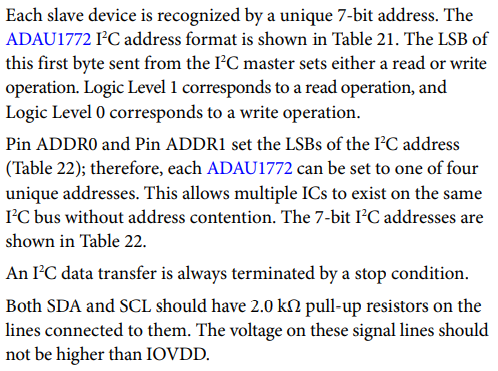

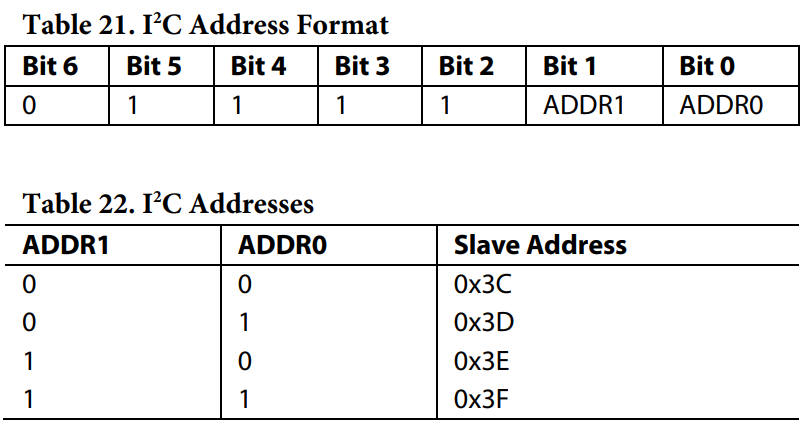

主机每次发送8位数据,其中最低的一位由主机发送标识读/写位。逻辑电平1是读,逻辑电平0是写。

通过I2C方式进行连接的从机,其设备地址是7位数(1-7,对应表21是bit0-bit6),表21提供了1772的设备地址,ADDR1

和 ADDR0

位置可以通过接入pin的方式自由设置,即输入引脚的电平不同,每个1772都能够拥有4个独特的地址。此类方式允许多块1772接入同一I2C总线。

- 即,默认情况下从机地址为

0x3C,可以设置成其他:0x3D,0x3E,0x3F。 - 每个SDA和SCL线都应该接入一个2.0KΩ的升压电阻,但不应该高过IOVDD。

相关问答

Q: what is the macro SIGMA_WRITE_DELAY supposed to do? Is it a simple delay? Why are there parameters regarding the device I2C address, data and length? A: This macro is used for applications that need to pause the data writes for a specific purpose. For example, if you need time for the PLL to be set before starting to write to the rest of the registers. It could be used as a simple delay, you’ll need to specify the device address always because some applications can require more than one DSP; the length is just the address byte length (could be 1 or 2 byte length) and data is the value in hex that represents the total time in milliseconds (that is up to the micro controller clock speed). The reason length is used, is that some DSPs work with one and some other require two address bytes.

<SigmaStudioFW.h> contains a lot of macros to be

defined. What I found by examinating all the code is that what macros

need to be defined depend on what you want to perform with your

microcontroller.

If you only need to load a DSP program with a call to default_download(), well, you only need (at least for the ADAU1761)

to implement the two macros:

SIGMA_WRITE_REGISTER_BLOCK

SIGMA_WRITE_DELAY

The first one is the basis of all the loading of data into program ram, parameter ram, and registers. The second one is only a delay (to be exact it serves to wait for the PLL to lock, in any case most of the times it can be implemented as a simple delay).

If you want to use sequences, that is to implement some control of the DSP running with your microcontroller, you will probably need to implement the other macros. In particular if you will control volume sliders you will need to implement the conversion macros for integer or float to the internal 5.23 representation. You can search elsewhere on the forum, I saw some of this code.

开发代码

ADI和Codec之间的I2C通信可以通过两种方式进行,第一种是操作21478上面的TWI寄存器,需要查看《HWR》以获取更多信息。第二种是学会控制引脚高低电平,通过高低电平模拟寄存器操控来读取和写入I2C设备。

在开发过程中,先使用的第一种方式对TWI寄存器进行操控,但发现21479中有某个寄存器无法写入,故放弃。下面提供第二种方式中需要用到的三个文件,分别是

TWI.h 、 TWI.c 、SigmaStudioFW.h

。经调试,以下代码可以正常收发数据,实现对从设备的读/写。

TWI.c

1 | /* |

TWI.h

1 | /* |

SigmaStudioFW.h

1 |

|